# Conductive Cu Paste as a Via Filling Material for Through Glass Via (TGV)

Yoshinori Ejiri, Masumi Sakamoto, Chiaki Shimizu, Naoyuki Kikuchi, Futoshi Oikawa, Masayoshi Nishimoto, Seiji Kai, Hiroshi Uragami Resonac Co., Ltd. Ibaraki, Japan ejiri.yoshinori.xikad@resonac.com

# ABSTRACT

We developed a Cu paste that can be used as a filling material for a through-glass via (TGV). A TGV substrate can be filled with Cu paste without voids by using the vacuum-press method. A Cu film with the lowest volume resistivity of approximately 3.5  $\mu\Omega$  · cm was obtained at 350 °C or higher in a hydrogen atmosphere. Daisy chain samples were prepared using TGV substrates filled with Cu paste, and reliability tests were conducted. The resistance changes of the daisy chain samples after the reliability tests [thermal cycle test (TCT) (-55/125 °C, 1000 cycles), high temperature storage test (HTST) (150 °C-1000 h, 260 °C-10 h), un-bias high accelerated stress test (HAST), pressure cooker test (PCT), and reflow cycle test (max. temp: 265 °C, 10 times, N<sub>2</sub>)] were within 3% of the initial value. Following electrolytic Cu plating, cracks occurred around the glass via. In contrast, the Cu paste was able to suppress the cracks in the via. The Young's modulus of the sintered Cu paste was approximately 30 GPa, which is less than half of the Young's modulus of the electrolytic Cu plating. The simulation results revealed that the low Young's modulus of the Cu paste suppressed the cracks at the edge of the Cu terminal and on the inner glass wall of the via. We found that the Cu paste can be applied to TGV substrates as a filling material.

Key words: Low-temperature metallization, Cu paste, Via filling, TSV, TGV, Organic substrate

### **INTRODUCTION**

Three-dimensional integrated circuits (3D ICs) and 2.5D ICs with silicon interposers are considered promising candidates for overcoming the limitations of Moor's law, owing to their advantages of low power consumption and high functional density<sup>1-2)</sup>. The interposer is a rigid insulator layer that serves as an interface between the high I/O of various logic and memory dies and a lower-density substrate. Through silicon vias (TSVs) are used in advanced 3D packaging solutions, such as the wafer-level packaging of microelectromechanical systems as well as silicon interposers<sup>3)</sup>.

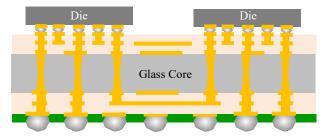

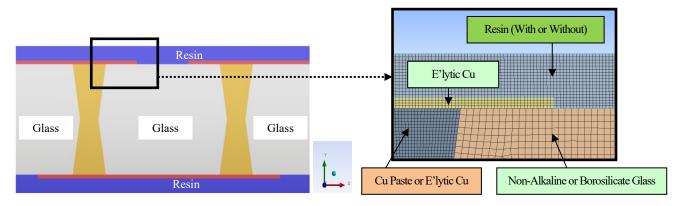

However, silicon interposers have several problems compared to glass interposers: (1) silicon is expensive because of the need for electrical insulation around the via sidewall; (2) the wafer size of silicon is limited; and (3) there are large CTE differences between Cu and silicon<sup>4</sup>). Accordingly, glass core substrates (Fig. 1) have been demonstrated as a replacement for Si interposers<sup>4-14)</sup>. Glass has relatively superior electrical properties, manageable CTE, and a low fabrication cost; moreover, it is manufactured with larger panel sizes and a wide range of thicknesses. Cu is preferred as a filling material in TSVs and TGVs because of its excellent electrical conductivity and superior ability to fill large structures. Cu filling by electroplating is one of the core critical procedures in the fabrication of TSV and TGV. Various studies have been conducted on plating conditions and additives<sup>15-21</sup>). However, the plating of larger TSV and TGV structures often results in voids in the Cu filling, a relatively thick outer surface layer plating, and low productivity.

Figure 1. Glass Core Substrate.

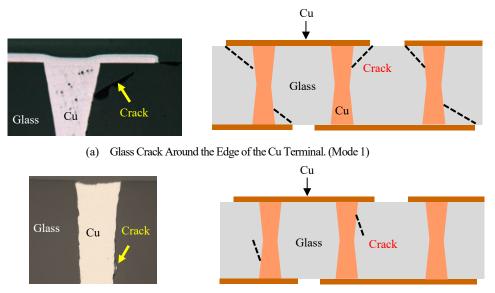

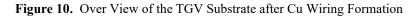

Regarding TGV, there are reports of cracks around vias<sup>22-24</sup>). In addition, a research example focusing on stress changes in an electrolytic Cu plating filled into glass vias was reported<sup>25-27</sup>). In our study, we observed that glass cracks occurred around the edge of the Cu terminal and on the via sidewalls (Fig. 2). We estimated that the glass cracks around the edge of the Cu terminal [Fig. 2 (a) (Mode 1)] were the same as those reported by Zhao<sup>22</sup>), and the cracks on the via sidewall were similar to those reported for TSV<sup>28, 29</sup>). Examples of using Cu paste<sup>30, 31</sup>), Ag paste<sup>32</sup>, and Ni rods<sup>33</sup>) as filling materials for TGV have been reported, but their effects on glass cracking and reliability evaluation have not been sufficiently investigated. Furthermore, it is known that sintered Cu paste has a lower Yang's modulus than bulk Cu<sup>34</sup>) or electrolytic Cu plating film<sup>35</sup>, and can be expected to

suppress cracks in glass. Therefore, we investigated the reliability of Cu paste as a filling material for TGV and the effect of Cu paste on crack suppression in glass.

(b) Glass Crack on the Via Sidewall. (Mode 2)

#### EXPERIMENTS Process and Examination Items Volume Resistivity Measurement

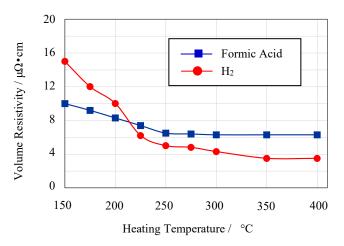

To investigate the effect of sintering conditions, Cu films with a thickness of 60  $\mu$ m were prepared, and the volume resistivity was measured. The Cu paste was sintered in formic acid or a 100% hydrogen atmosphere. The sintering temperature varied from 150 °C to 400 °C.

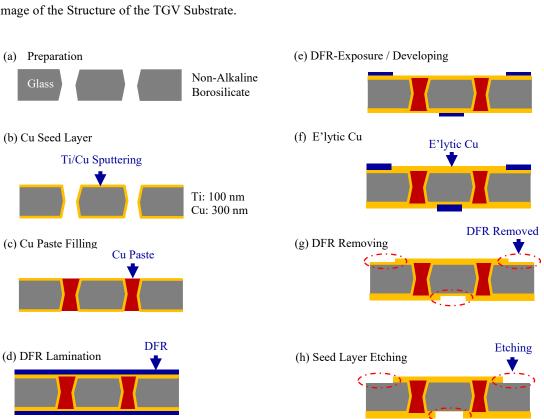

# Fabrication of TGV Substrate using Cu Paste

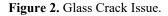

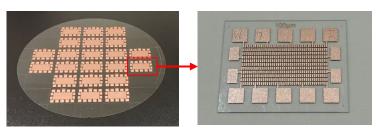

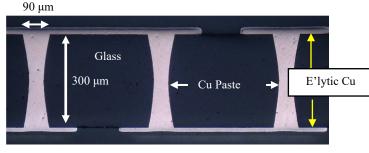

An overview of the glass wafer is provided in Fig. 3. TGV substrates with a diameter of 90  $\mu$ m and a thickness of 300  $\mu$ m were filled with Cu paste. The components of the TGV substrates are listed in Table 1. Figure 4(a) shows a cross-sectional image of a TGV substrate after the vias were filled with Cu paste. Electrolytic Cu terminals with a thickness of 10  $\mu$ m can be seen on the glass substrate, and the substrate is

Figure 3. Over View of the Glass Wafer.

Table 1. TGV Substrate Components

| Items         | Details                      |

|---------------|------------------------------|

| Kind of Glass | Non-Alkaline, Borosilicate   |

| Seed Layer    | Ti: 100 nm, Cu: 300 nm       |

| Via Filling   | •E'lytic Cu 10 µm + Cu Paste |

|               | •Only Cu Paste               |

| Resin Coated  | with, without                |

400 µm

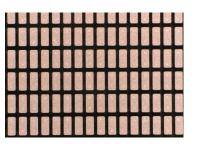

(b) Top View Image of the Cu Terminals

Figure 4. Image of the Structure of the TGV Substrate.

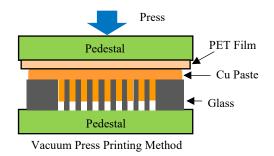

covered with a 30 µm thick epoxy resin film. Figure 4(b) shows a top view of the Cu terminals. Figure 5 shows the Cu wiring formation method on a TGV substrate using Cu paste. Two glasses with different coefficients of thermal expansion (CTEs) were prepared: non-alkaline glass (CTE: 3.2 ppm/°C) and borosilicate glass (CTE: 7.2 ppm/°C) (Fig. 5 (a)). Ti/Cu seed layers (Ti: 100 nm; Cu: 300 nm) formed on the glass substrate (Fig. 5 (b)). The glass vias were filled with Cu paste (Fig. 5 (c)). As shown in Fig. 6, the Cu paste was applied to the PET film and pressed under vacuum at a pressure of 0.3 MPa. The TGV substrates were sintered at 250 °C for 1 h under a 100% hydrogen atmosphere. A dry film resist (DFR) was laminated onto the substrate (Fig. 5 (d)). The DFR was exposed and developed (Fig. 5 (e)), and the openings in the DFR were electroplated with Cu (Fig. 5 (f)). After removing the DFR (Fig. 5 (g)) and etching the Ti/Cu seed layer (Fig. 5 (h)), daisy chain samples with Cu pads that had formed on both sides of the glass were obtained.

Proceedinds Straft Wiring En mation - Mathada, Rosemont, IL, USA.

Figure 6. Process of Filling Holes with Cu Paste.

### **Comparison of Conductive Resistance Value**

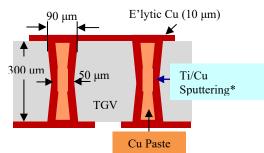

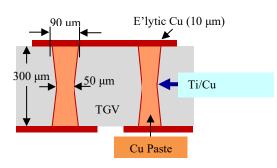

To compare the conductive resistance values when electrolytic Cu plating and Cu paste were applied to the vias, TGV substrates consisting of approximately 1,000 vias with the structure shown in Fig. 7 were fabricated. In the case of electrolytic Cu plating and Cu paste (Fig. 7 (a)), Ti/Cu seed layers (Ti: 100 nm, Cu: 300 nm) formed on the surface of the glass substrate, and electrolytic Cu plating was applied to a thickness of 10 µm to create conformal vias. The conformal vias were filled with sintered Cu paste. The Cu on the glass substrate surface was polished using chemical mechanical polishing (CMP) to expose the glass surface. After Ti/Cu seed layers (Ti: 100 nm, Cu: 300 nm) formed, a 10 µm thick electrolytic Cu pattern was created on the glass surface by the semi-additive method. To prepare the Cu paste (Fig. 7 (b)), the substrate was prepared according to the process shown in Fig. 5.

(a) E'lytic Cu  $10\mu m$  + Cu Paste

# (b) Only Cu Paste

**Figure 7.** Comparison of the Via Structure using Different Via Filling Methods. \* Ti: 100 nm, Cu: 300 nm

#### **Reliability Test**

The daisy chain samples were subjected to a reliability test [TCT, HTST, HAST, PCT, and reflow (air atmosphere))]. The test conditions are presented in Table 2.

Table 2. Reliability Test Conditions.

| Test Items               | Details                      |

|--------------------------|------------------------------|

| TCT                      | -55/125 °C / 1000 cycles     |

| HTST                     | 150 °C/1000 h                |

| 1151                     | 260 °C/10 h                  |

| HAST                     | 130 °C, 85%RH / 96 h         |

| PCT                      | 121 °C, 100%RH / 96 h        |

| Reflow (N <sub>2</sub> ) | Peak Temp. 265 °C / 10 times |

# Young's Modulus Measurement of Cu Film Obtained by Cu Paste

Cu films with a thickness of 200  $\mu$ m obtained at 250 °C for 1 h under a 100% hydrogen atmosphere were prepared, and the Young's modulus was measured. The Young's modulus was measured in air at room temperature using a device manufactured by Nippon Techno Plus (JE2-RT) using the resonance method.

#### **Finite Element Simulation**

The ANSYS workbench software was used to analyze the stress caused by the shrinkage deformation of glass and Cu, which have different coefficients of thermal expansion. A 3D CAD model of the TGV substrate was used, as shown in Fig. 8. Figure 8(a) shows a cross-sectional image of the TGV structure, and Fig. 8(b) shows the mesh of the model and boundary conditions. A static analysis was performed on samples with and without the resin coating. In the analysis, a uniform temperature distribution was applied to multiple components with different thermal expansion coefficients, and the entire structure contracted owing to the change in temperature. An overview of the analysis conditions and material properties is presented in Tables 3 and 4.

(a) Cross Sectional Image of the TGV Structure

Figure 8. CAD Model of the TGV Structure

Table 3. Thermal Stress Analysis Conditions

| Simulation Elements | 3-D 20-node solid element                             |  |  |  |  |

|---------------------|-------------------------------------------------------|--|--|--|--|

|                     | The number of setting nodes: 145635                   |  |  |  |  |

|                     | 3-D Model                                             |  |  |  |  |

| Boundary Condition  | Completely restrain the bottom left edge of the glass |  |  |  |  |

|                     | Friction-free support for the left side of the glass  |  |  |  |  |

| Loading Condition   | -180 °C heat load on all parts                        |  |  |  |  |

| Material Properties | Assumed as an elastic body                            |  |  |  |  |

Table 4. Material Properties of the TGV Substrate Components

| Items               | E'lytic Cu | Cu Paste |       | Glass        |              |  |  |

|---------------------|------------|----------|-------|--------------|--------------|--|--|

|                     |            |          | Resin | Non-Alkaline | Borosilicate |  |  |

| Yang's Modulus(Gpa) | 123        | 60       | 7.5   | 73.6         | 72.9         |  |  |

| Poisson's Ratio     | 0.35       | 0.25     | 0.29  | 0.23         | 0.21         |  |  |

| CTE(ppm/°C)         | 16.5       | 16.5     | 23    | 3.2          | 7.2          |  |  |

#### **RESULTS AND DISCUSSION** Volume Resistivity of Cu Films

The volume resistivity of the Cu films as a function of sintering temperature and atmosphere is shown in Fig. 9. Comparing the films formed in formic acid and hydrogen atmospheres, we found that the hydrogen atmosphere was effective in obtaining a Cu film with a lower volume resistivity. For temperatures above 225 °C, a lower volume resistivity film was obtained in the hydrogen atmosphere compared to that in the formic acid atmosphere. Furthermore, a film with the lowest volume resistivity of approximately 3.5  $\mu\Omega$  · cm was obtained at 350 °C or higher in the hydrogen atmosphere. For temperatures at and below 200 °C, it was found that, compared to a hydrogen atmosphere, a formic acid atmosphere is effective for obtaining Cu films with a low volume resistivity. The film with the lowest volume resistivity at 150 °C was obtained in the formic acid atmosphere.

(b) Enlarged View of the Mesh Model

**Figure 9.** Volume Resistivity of Cu Films as a Function of Sintering Temperature and Atmosphere.

# Fabrication of Daisy Chain Substrate Sample using Cu Paste

An overview of the TGV substrate after the Cu wiring formation is shown in Fig. 10. A TGV substrate can be filled with Cu paste without voids using the vacuum-press method (Fig. 10 (c)). This sample was manufactured using the method shown in Fig. 5, and electrolytic Cu plating was performed on the buried Cu paste using a semi-additive process.

# Comparison of Conductive Resistance by Via Filling Method

We compared the conductive resistance of two samples: one with 10  $\mu$ m of electrolytic Cu plating on the inner wall of the via and filled with Cu paste (Fig. 7 (a)) and another that was only filled with Cu paste (Fig. 7 (b)). Cu paste was sintered at 250 °C in a hydrogen atmosphere. It was found that for both substrates, the conductive resistance was 5.2  $\Omega$  (about 1,000 vias), and there was no difference in resistivity. These results reveal that it is possible to produce TGV substrates consisting of low-resistance Cu wiring using Cu paste.

# Initial Evaluation of Glass Cracks caused by TGV Substrate Components

In order to evaluate the influence of the TGV substrate components on the occurrence of glass cracks, the TGV substrates with the configuration shown in Table 5 were fabricated and evaluated by the TCT test (-55/125 °C, 20 cycles). As shown in Fig. 11, glass cracks occurred near the Cu terminal edge (Fig. 2a, mode I) on the non-alkaline glass without the resin-coated substrate (Table 5, No.1 condition). Glass cracks on the via sidewall (Fig. 2b, Mode II) were not observed in this test.

Table 5. Reliability Test Results of TGV Substrates.

| Items                                          | No.               |                    |                                   |          |  |  |

|------------------------------------------------|-------------------|--------------------|-----------------------------------|----------|--|--|

| items                                          | 1                 | 2                  | 3                                 | 4        |  |  |

| Kind of Glass                                  |                   | lkaline<br>ppm/°C) | Borosilicate<br>(CTE: 7.2 ppm/°C) |          |  |  |

| Resin Coated                                   | without           | with               | without                           | with     |  |  |

| Via Filling                                    | Only Cu Paste     |                    |                                   |          |  |  |

| Reliability Test<br>TCT: -55/125 °C, 20 Cycles | Crack<br>(Mode 1) | No Crack           | No Crack                          | No Crack |  |  |

(a) External View of the Substrate

(b) Top View of the Cu Terminal

(c) Cross Sectional View

**Figure 11.** Glass Cracks near the Cu Terminal Edge (Mode I) after TCT. Glass: Non-Alkaline, Resin Coated: without (Table5, No.1)

Compared to non-alkaline glass (CTE: 3.2 ppm/°C), the CTE of borosilicate glass (CTE: 7.2 ppm/°C) is closer to that of Cu (CTE: 16.5 ppm/°C). We infer that the smaller difference in the CTE between glass and Cu is an important factor in preventing the generation of glass cracks.

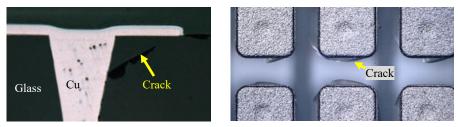

#### **Reliability Test**

TGV substrates composed of borosilicate glass filled with Cu paste and coated with resin were used for the reliability tests. The TGV substrates were subjected to a reliability test (Table 2), and the rate of change in the conductive

Figure 12. TCT Results of the TGV Substrate.

resistance was within 3% in all the tests. The TCT results are shown in Fig. 12. We found that the Cu paste can be applied to TGV substrates as a filling material.

#### **Finite Element Simulation**

To investigate the root cause of the glass cracks around the edge of the Cu terminal (Mode 1) and on the via sidewall (Mode 2), we conducted a stress analysis around the via on the TGV substrates.

### (1)Glass Crack around Edge of Cu Terminal (Fig. 2 (a), Mode 1)

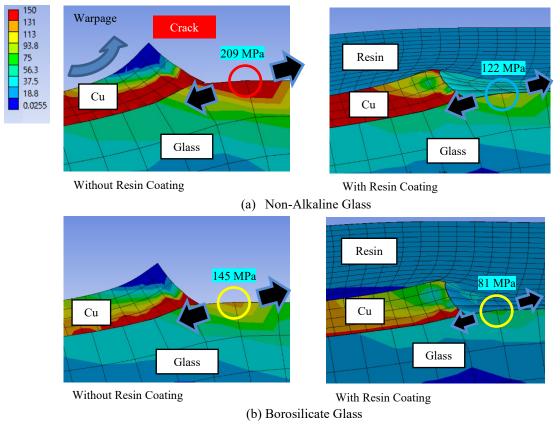

Figure 13 shows the stress analysis results around the edge of the Cu terminal for different types of glass with and without resin coating. Only the Cu paste was used as the filling material. In the case of the non-alkaline glass without a resin coating (Fig. 13 (a)), the stress in the glass near the Cu terminal was 209 MPa, which was higher than that under other conditions. Coating with the resin significantly reduced the stress from 209 to 122 MPa (Fig. 13 (a), right figure). We inferred that the soft resin absorbed the warping of Cu, suppressing the warping of the glass and preventing glass cracks. Furthermore, by changing the glass from nonalkaline to borosilicate glass,

**Figure 13.** Stress Analysis for Different Types of Glass and with or without the Resin Coating. Via Filling Material: Cu Paste

the maximum stress around the edge of the Cu terminal was reduced (Fig. 13 (b)). A comparison of the stress values in glass at the edge of the Cu terminals (Mode 1) due to differences in the via filling materials is shown in Table 6. Electrolytic Cu plating assumes a filled via (i.e., full filling with electrolytic Cu plating). It was found that the stress values were lower with the Cu paste than with the filled via formed by electrolytic Cu plating. The Young's modulus of the Cu film sintered in hydrogen at 250 °C and measured by the resonance method was 30 GPa. The Young's modulus of an electrolytic Cu-plating film is reportedly approximately 110 GPa or more<sup>35)</sup>. We infer that the reduction in the Young's modulus caused by the Cu paste relative to the electrolytic Cu plating suppresses cracks in the glass around the Cu terminal.

#### (2)Glass Crack on Via Sidewall (Fig. 2 (b), Mode 2)

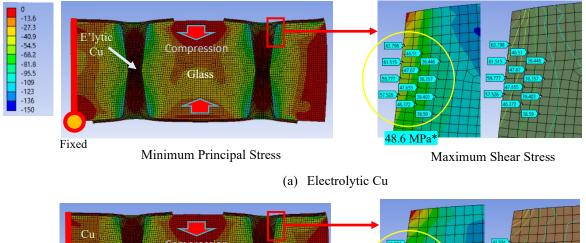

To clarify the effect of the Cu paste on the suppression of internal cracks, the stress on glass substrates was analyzed when electrolytic Cu plating and Cu paste were applied as filling materials. Fig. 14 shows the analysis results of the minimum principal stress around the entire via and the maximum principal stress on the inner wall of the via when the resin was not coated with non-alkaline glass. In the case of electrolytic Cu plating, the maximum shear stress (average value of 12 points) was 48.6 MPa (Fig. 14 a), but that of Cu paste was 32.6 MPa (Fig. 14 b). We infer that the Cu paste with a low Young's modulus has a lower glass shear stress and suppresses internal glass cracking better than electrolytic Cu. Table 7 shows the maximum shear stress for the electrolytic Cu and Cu pastes, depending on the type of

**Table 6.** Comparison of the Maximum Stress Values in Glass at the Edge of Cu Terminals (Mode 1) due to Differences in Via Filling Materials.

| Items               | E'lytic Cu (Filled Via) |      |              |      | Cu Paste     |      |              |      |

|---------------------|-------------------------|------|--------------|------|--------------|------|--------------|------|

| Kind of Glass       | Non-Alkaline            |      | Borosilicate |      | Non-Alkaline |      | Borosilicate |      |

| Resin Coated        | without                 | with | without      | with | without      | with | without      | with |

| Maximum Stress(MPa) | 229                     | 166  | 159          | 115  | 209          | 122  | 145          | 81   |

**Figure 14.** Stress Analysis for Different Types of Via Filling Materials. Glass: Non-Alkaline Glass, Without Resin Coating \* Average Maximum Share Stress (12 Point)

| Items                      | E'lytic Cu (Filled Via) |      |              |      | Cu Paste     |      |              |      |

|----------------------------|-------------------------|------|--------------|------|--------------|------|--------------|------|

| Kind of Glass              | Non-Alkaline            |      | Borosilicate |      | Non-Alkaline |      | Borosilicate |      |

| Resin Coated               | without                 | with | without      | with | without      | with | without      | with |

| Maximum Shear Stress (Mpa) | 48.6                    | 45.9 | 33.4         | 31.9 | 32.6         | 30.2 | 22.7         | 21.1 |

Table 7. Maximum Shear Stress Analysis for the Inner Wall of Glass (Mode 2).

glass and resin coating. The maximum shear stress was reduced the most using borosilicate glass, coating with resin, and applying a Cu paste.

The simulation results revealed that the stress on the glass at the edge of the Cu terminal and on the inner wall of the via could be reduced by 1) using a glass material with a CTE close to that of Cu, 2) using Cu paste rather than electrolytic Cu plating as the via-filling material, and 3) coating the TGV substrate surface with resin.

# CONCLUSION

We have developed a Cu paste that can be used as a filling material for TGVs. The following key conclusions were drawn.

- (1) The film with the lowest volume resistivity of approximately 3.5  $\mu\Omega$  · cm was obtained at 350 °C or higher in the hydrogen atmosphere.

- (2) A TGV substrate can be filled with Cu paste without voids by using the vacuum-press method.

- (3) The rate of change in the conductive resistance of the substrate was found to be within 3% of the initial value after the reliability test.

- (4) We infer that the smaller difference in the CTE between glass and Cu is an important factor in preventing the generation of glass cracks.

- (5) The simulation results revealed that the low Young's modulus of the Cu paste suppressed the cracks at the edge of the Cu terminal and on the inner wall of the via.

# REFERENCES

- [1] S. W. Ho, S. W. Yoon, Q. Zhou, K. Pasad, V. Kripesh, J. H. Lau, "High RF performance TSV silicon carrier for high frequency application", In Proceedings of the Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 27–30 May 2008, pp. 1946~1952.

- [2] S. Koester, A. Young, R. Yu, S. Purushothaman, K. Chen, D. La, N. Rana, L. Shi, M. Wordeman and E. Sprogis, "Wafer-level 3D integration technology", IBM J. Res. Dev., 52, 2008, pp. 583~597.

- [3] J. H. Lau, "Recent Advances and Trends in Fan-Out Wafer/Panel-Level Packaging", ASME Journal of Electronic Packaging, 141(12), 2019, p. 040801.

- [4] R. Tummala et al., "Glass Panel Packaging, as the Most Leading-Edge Packaging: Technologies and Applications," Proceedings of SMTA Pan Pacific Microelectronics Symposium, HI, USA, 2020, pp. 1-5.

- [5] T. Shi et al., "First demonstration of panel glass fan-out (GFO) packages for high I/O density and high frequency multi-chip integration," Proc. IEEE 67th Electron. Compon. Technol. Conf., 2017, pp. 41–46.

- [6] B. Singh et al., "Board-Level Thermal Cycling and Drop-Test Reliability of Large, Ultrathin Glass BGA Packages for Smart Molile Applications," IEEE Transactions of Components, Packaging and Manufacturing Technology, Vol. 7, No. 5, May 2017.

- [7] S. Ravichandran, M. Kathaperumal, M. Swaminathan, and R. Tummala, "Large-body-sized glass-based active interposer for highperformance computing," Proc. IEEE 70th Electron. Compon. Technol. Conf., 2020, pp. 879–884.

- [8] S. Kuramochi et al., "High Speed Data Transmission Characteristics on Glass Based Interposer, Proceedings of SMTAI, 2021, pp.49-58.

- [9] S. Mitarai et al., "Physical and Thermal Characteristics of the Advanced Package with Glass Core Substrate, Proceedings of ICEP, 2024, pp. 174-175.

- [10] S. Takahashi et al., "Development of Through Glass Via (TGV) Formation Technology Using Electrical Discharging for 2.5/3D Integrated Packaging," Proc. IEEE 63th Electron. Compon. Technol. Conf., 2013, pp. 348-352.

- [11] M. Töpper et al., "3-D Thin Film Interposer Based on TGV (Through Glass Vias): An Alternative to Si-Interposer," Proc. IEEE 60th Electron. Compon. Technol. Conf., 2010, pp. 66-73.

- [12] R. Delmdahl and R. Paetzel, "Laser Drilling of High-Density Through Glass Vias (TGVs) for 2.5D and 3D Packaging", *J. Microelectron. Packag. Soc.*, 21(2), 2014, pp. 53~57.

- [13] M. J. Laakso, J. Liljeholm, A. C. Fischer, G. Stemme, T. Ebefors, and F. Niklaus, "Maskless manufacturing of through glass vias (TGVs) and their test structures", *In Proceedings of IEEE 30th Int. Conf. Micro Electro Mech. Syst. (MEMS)*, Las Vegas, NV, USA, Jan. 2017, pp. 753~756.

- [14] T. Chaloun et al., "RF Glass Technology Is Going Mainstream: Review and Future Applications", *IEEE Journal of Microwaves*, Vol. 3, No.2, April 2023.

- [15] Y. Chang et al., "Communication—Defect-Free Filling of High Aspect Ratio Through Vias in Ultrathin Glass", Journal of The Electrochemical Society, 166 (1) D3155-D3157 (2019).

- [16] Fei Zhao et al., "Improvement on Fully Filled Through Silicon Vias by Optimized Sputtering and Electroplating Conditions", Materials 2019, 12, 3713.

- [17] P. Ogutu et al., "Superconformal Filling of Through Vias in Glass Interposers", ECS Electrochemistry Letters, 3 (8) D30-D32 (2014).

- [18] W. Shen et al., "Three-Dimensional Integrated Circuit (3D IC) Key Technology: Through-Silicon Via (TSV)", Shen and Chen Nanoscale Research Letters, 2017, pp. 1-9.

- [19] D. Josell, L. A. Menk, A. E. Hollowell, M. Blain and T. P. Moffat, "Bottom-up Copper Filling of Millimeter Size Through Silicon Vias", *Journal of Electrochemical Society*, 166(1), 2019, pp. D3254~D3258.

- [20] Q. S. Zhu, X. Zhang, C. Z. Liu and H. Y. Liu: "Effect of Reverse Pulse on Additives Adsorption and Copper Filling for Through Silicon Via", *Journal of The Electrochemical Society*, 166(1), 2019, pp. D3006~D3012.

- [21] R. P. Schmitt, L. A. Menk, E. Baca, J. E. Bower, J. A. Rpmero, M. B. Joordan, N. Jackson and A. E. Hollowell: "Void-free Copper Electrodeposition in High Aspect Ratio, Full Wafer Thickness Through-Silicon Vias with Endpoint Detection", *Journal of The Electrochemical Society*, 167, 2021, p. 162517.

- [22] J. Zhao et al., "Thermo-Mechanical Reliability Study of Through Glass Vias in 3D Interconnection", Micromachines 2022, 13, 1799.

- [23] C. Okuro et al., "Understanding and eliminating thermomechanically induced radial cracks in fully metallized through-glass via (TGV) substrates", Microelectronics Reliability 120 (2021).

- [24] Y. Sato et al., "Laser-drilling formation of through-glass-via (TGV) on polymer-laminated glass", Journal of Materials Science: Materials in Electronics (2019).

- [25] K. Pan et al., "High-Temperature Constitutive Behavior of Electroplated Copper TGV Through Numerical Simulation", IEEE Transactions on Components, Packaging and Manufacturing Technology, Vol. 13, No. 11, 2023.

- [26] K. Pan et al., "In-situ temperature-dependent characterization of copper through glass via (TGV)", Microelectronics Reliability 129 (2022).

- [27] A. Benali et al., "Analytical and Finite Element Modeling of Through Glass Via Thermal Stress", Microelectronic Engineering 151 (2016) 12-18.

- [28] S. Chen et al., "Effect of temperature cycling on the leakage mechanism of TSV liner", Microelectronics Reliability, 141 (2023).

- [29] H. Kitada et al., "Thermal Stress Destruction Analysis in Low-K Layer by Via-last TSV Structure," Proc. IEEE 65th Electron. Compon. Technol. Conf., 2015, pp. 1840–1845.

- [30] X. hang et al., "Fabrication of Capacitive Micromachined Ultrasonic Transducers with Through-Glass-Via Interconnects", 2015 IEEE International Ultrasonics Symposium Proceedings, Conference Paper.

- [31] S. Takahashi et al., "Development of TGV Interposer for 3D IC", 46th International Symposium on

Microelectronics (IMAPS 2013), pp. 631-634.

- [32] C. Yu et al., "Application of Through Glass Via (TGV) Technology for Sensors Manufacturing and Packaging", Sensors 2024, 24, 171.

- [33] M. J. Laakso et al., "Through-Glass Vias for Glass Interposers and MEMS Packaging Applications Fabricated Using Magnetic Assembly of Microscale Metal Wires", IEEE Access, Vol. 6, 2018.

- [34] T. Ishizaki et al., "Young's Modulus of a Sintered Cu Joint and its Influence on Thermal Stress", Microelectronics Reliability, Vol. 76-77, 2018, pp. 405-408.

- [35] S. Kohara et al., "Analysis of Process Dependent Mechanical Properties of Sintered Copper Nanoparticle Pillars for the Plating-free Bumping by Finite Element Method", 21<sup>st</sup> IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (iTherm) 2022.