# Complex Board Design Induced Solder Separation Failure: Mechanism and Mitigation Using Low Melting Temperature Interconnects

Tae-Kyu Lee, Gnyaneshwar Ramakrishna Cisco Systems CA, USA taeklee@cisco.com

Jonghyun Nam, Daljin Yoon, and Heera Roh SK Hynix Icheon, Korea

### ABSTRACT

The increase of functionality and performance in electronic systems and devices induce more complex printed circuit board design features with more Cu layer counts, increased thickness, and with a demand for less impact to the highspeed signals. These combinations drive the PCB design to configurations including via-in pad platted over (VIPPO) with back-drill process, which resulted in a mixture of various stress distributions in a given printed circuit board. Recent studies revealed that these mixed design features can induce failure during a second reflow at the solder joint interface known as solder separation. Through a series of insitu resistance measurements during reflow, the accurate separation location and temperature are identified per design configuration and solder joint material combination. A 10x15mm BGA component with 10x20 array solder balls were assembled on 28 Cu-layered 140mil thickness boards, which contain a mixture of VIPPO and VIPPO+back-drilled pads compared to a full VIPPO pad design as a baseline. The assembled boards were subject to in-situ resistance measurements during second reflow. The segmented daisy chains per component allowed the detection of solder separation during reflow at the exact solder joint location, which are associated with the failure symptoms. The failure signature was detected at 210-212°C during heating cycle at solder joint locations, which are adjacent to solder joints with higher z-axis expansion, in this case full VIPPO location adjacent to back-drilled VIPPO pad locations. Three different solder alloys were selected to investigate the sensitivity to solder separation defects along with the evaluation per longterm thermal cycling performance. The results indicated that the separation defect in SAC305 can be mitigated by using SAC305+SnBiAg low melting temperature (LTS) hybrid solder joint configuration and full LTS configuration. The presented study elaborates the parameters associated with the solder separation failure per board design configuration, and provides the potential solution to mitigate the failure. An indepth analysis on the solder joint microstructure utilizing Electron-backscattered diffraction (EBSD) supports the test results leading to the mechanism associated with the solder separation defect failure.

Key words: via-in pad plated over (VIPPO), Multi-axis loading, Solder separation defect, EBSD

# **INTRODUCTION**

Recent industry demands for higher signal integration and faster signal speed in high performance electronic systems not only drive the innovation in the ASIC and component level, but also requires a vast innovation in printed circuit board design to accommodate more complex and higher density structure configuration, which influence the board thickness increase with higher Cu layer count and a higher rate of via-in-pad implementation. With a higher density of Cu vias inside the printed circuit board, the thermal cycling performance of the ball grid array (BGA) components varies with the via configuration since the localized deformation is altered due to the different Cu distributions. Cu vias can be drilled in any available real estate on the PCB and the signal traced to and from the designated input and output within and between interconnected PCB layers [1,2]. The via-in-pad configuration permits the use of subsurface layers for routing purposes and eliminates trace routing between pads [3]. These are implemented with copper plated on the surface, commonly referred to as via-in-pad plated over (VIPPO). VIPPO vias are incorporated into PCB designs either as unevenly distributed VIPPO vias, as blanket VIPPO vias and back-drilled VIPPO vias. In a mixed VIPPO configuration, PCB vias are designed to contain a mixture of dog-bone,

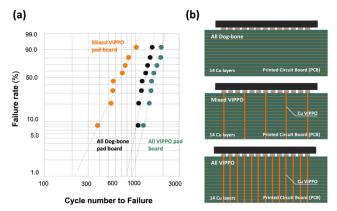

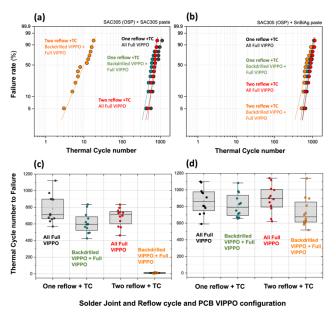

**Figure 1.** Thermal cycling result Weibull plot (a) and PCB configuration (b)

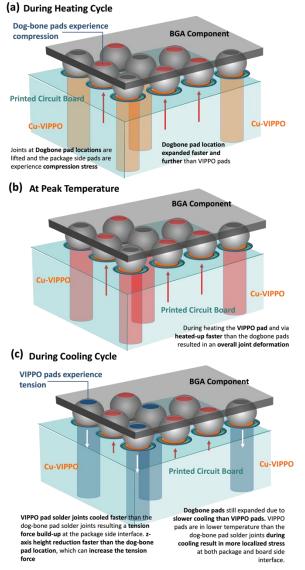

**Figure 2.** Solder separation defect development mechanism. (a) during heating cycle, (b) at peak temperature, and (c) during cooling cycle

through-hole, and VIPPO vias. Under the blanket design, all vias on the PCB board have the VIPPO configuration and

either have the full VIPPO from the PCB surface to the bottom or back-drilled to a certain Cu layer to eliminate the non-functional Cu, then filled with epoxy filler and capped with Cu [4]. The structures can increase the component density and functionality and improve the signal integrity and thermal management [4,5]. With the implementation of various via structures, a detailed monitoring methodology for each localized solder interconnect is needed to understand the overall thermomechanical and mechanical performances per solder joint. For example, Perng et al. published an in-situ monitoring methodology in which the electric discontinuity of each BGA solder joint is monitored in real time as the boards undergo an assembly reflow [6,7]. This provides a log of resistance versus time with relation to temperature, enabling the determination of the exact failure temperature and specific localized solder interconnect with unevenly distributed VIPPO configurations [6,7]. The unevenly distributed VIPPO PCB not only affects the solder joint stability at the assembly reflow, it also affects the thermal cycling performance since the z-axis expansion rates are different per VIPPO and non-VIPPO pad locations. Figure 1 shows an earlier published SAC305 thermal cycling performance data with unevenly distributed VIPPO PCB, compared to dog-bone only and all VIPPO PCB configurations. A significant degradation in thermal cycling performance is observed. The degradation mechanism is schematically explained in Figure 2. In the case of the mixed VIPPO configuration, the PCB material expands more in the z-axis direction than full Cu VIPPO pad locations; thus, with heating during thermal cycling, the dog-bone pad solder joint package side interface will experience a higher compression force than VIPPO pad joints. In the same time window, the full VIPPO pad solder joints will heat up faster than the dogbone pad solder joints and have a higher possibility for overall tension force build up and deformation. After reaching the peak temperature cycle region, the test vehicle begins to cool down; the VIPPO pad solder joints cool faster than the dog-bone pad solder joints, resulting in a further tension force build-up at the package side interface and a zaxis height reduction faster than at the dog-bone pad locations, which can increase the tension force at the VIPPO pad joint locations. Additionally, the VIPPO pad solder joints are at a lower temperature than the dog-bone pad solder joints during cooling, resulting in a more localized stress at both package and board side interface, which ultimately provides a driving force for earlier crack initiation and crack propagation with vertical stress accumulation. To follow-up the recent study on unevenly distributed stress in PCB impact on solder joint stability, this study presented here focused on the back-drilled VIPPO + full VIPPO configuration. The joint interconnect resistances are in-situ monitored during the second reflow to identify the solder separation defect occurrence and the exact temperature when the separation defect occurs. Given the observation that solder separation in SAC305 occurs at 210-212°C, a possibility of mitigating the defect by applying a lower peak temperature reflow utilizing Low melting Temperature solder material (LTS) is considered and tested. Full Sn-Bi-In eutectic (LTS) solder joints along with SAC305+LTS hybrid joints are observed and compared to full SAC305 joint baseline. Further, the thermal cycling behavior of each solder joint material configuration with back-drilled VIPPO + full VIPPO PCB configuration with that of evenly distributed full VIPPO PCB is compared. Microstructural analysis with polarized imaging and electron backscattered diffraction (EBSD) were used to observe and identify the evolution of localized strains in the microstructure during testing.

### **EXPERIMENTAL PROCEDURE**

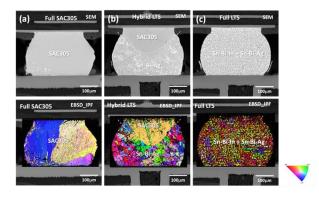

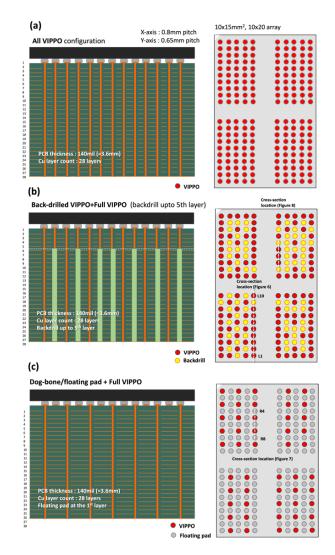

The BGA components used in this study are 10x20 solder ball array 10x15mm<sup>2</sup> components with 0.8 mm pitch to the X-axis and 0.65mm pitch to the Y-axis. Components have three different solder joint alloy configurations: 300 µm in diameter SAC305 solder balls which are assembled with either SAC305 paste (full SAC305) or Sn-Bi-Ag paste (hybrid LTS), 300 µm in diameter Sn-Bi-In solder balls which are assembled with Sn-Bi-Ag paste (full LTS). The solder balls are supplied by MK Electron and the SAC305 and Sn-Bi-Ag solder paste are supplied by Indium corporation. Components are assembled onto 140mil 370HR material printed circuit boards (PCB) with 28 layers of copper and a total thickness of 140mil (3.6 mm). A reflow profile with a 240°C peak temperature and a holding time above the liquidus (TAL) temperature of 90 seconds was used for the full SAC305 reflow and a 185°C peak temperature with 90 seconds TAL was used for hybrid LTS and full LTS assembly. Figure 3 shows the initial state microstructure after board assembly per solder joint configuration. The PCB pads are SMD with three different via-in-pad configurations: All full VIPPO (without backdrilling), back-drilled VIPPO + full VIPPO combination and with both dog-bone/floating pad and full VIPPO mixed configuration. Figure 4 presents the three different PCB configurations, which were used in this study. As shown in Figure 4(a), all pads are full VIPPO without back-drilled locations. The back-drilled location indicated in Figure 4(b) are back-drilled up to the 5th layer. The back-drilled pad locations are shown in yellow circles. The dog-bone/floating pad configuration has the pad entirely in the first Cu layer, mixed with full VIPPO pads connected from the first Cu layer pad to the bottom layer as shown in Figure 4(c). All components have full and segmented daisy chain for in-situ resistivity measurement during second reflow. The second reflow per solder joint configuration and reflow profile was applied in a desktop reflow oven. For data monitoring and accumulation, a Hioki LR8401-20 system was used for measuring the temperature and each daisy chain resistance with 200ms data collection intervals. High Pb solder (10Sn-88Pb-2Ag) with a melting temperature of 268-299°C (solidus-liquidus) and high temperature silicon coated Cu wire are used and insulating sleeves are used to prevent the Cu wire heating. Thermal cycling was performed with a 0 to 100°C

**Figure 3.** Initial microstructure right after board assembly. SEM image and EBSD-IPF image per joint configuration (a) Full SAC305 joint (SAC305 ball + SAC305 paste), (b) Hybrid LTS (SAC305 ball + Sn-Bi-Ag paste), and (c) Full LTS (Sn-Bi-In ball + Sn-Bi-Ag paste).

**Figure 4.** Three schematically shown PCB test board VIPPO configurations. Side view and top view. (a) Full VIPPO configuration, (b) Back-drilled VIPPO + Full VIPPO configuration, and (c) Dog-bone/Floating pad + Full VIPPO configuration.

thermal cycle with 10°C/min heating and cooling rate and a dwell time of 10 minutes. A datalogger was used to monitor and collect the continuous resistivity for each channel, and the failure criterion per component was set at a 20% increase in resistivity in five successive cycles using the standard JESD22-A104D [9,10]. Selected samples after first reflow assembly, second reflow applied and thermal cycled to failure were subjected microstructure analysis. Crosssectional analysis was carried out using optical microscope bright field and polarized imaging. Further microstructural analysis of the solder joints was performed using a scanning electron microscope (SEM) equipped with an electron backscattered diffraction (EBSD) high-speed detector (Oxford Instrument), and the images were analyzed with the analysis Aztec and Aztec Crystal software.

#### **RESULTS AND DISCUSSION**

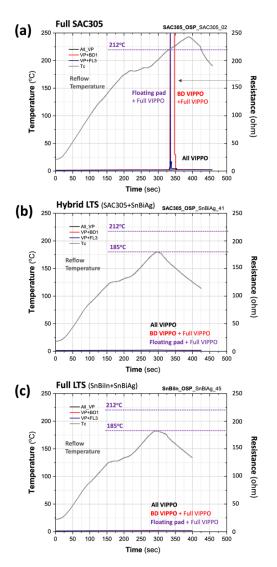

The in-situ resistance measurement during the second reflow is shown in Figure 5. Figure 5(a) is the temperature and resistance data for the full SAC305 configuration. The resistance for the full VIPPO only component does not show an open during the entire reflow cycle, but the back-drilled VIPPO + full VIPPO PCB and the dog-bone/floating pad + full VIPPO configurations show a sudden resistance increase at 212°C during heating. The open chains then show a reconnection and resistance decrease to the initial value before reaching to the peak temperature and maintaining the connection. It is important to note that the resistance at room temperature is the same as the initial resistance value, thus the detection of whether the component has a solder separation defect is hard to detect after assembly.

**Figure 5.** In-situ resistance measurement plot during second reflow. Temperature and resistance per VIPPO configuration. (a) Full SAC305 joint component, (b) Hybrid LTS, and (c) Full LTS component

**Figure 6.** Optical polarized image of Full SAC305 joint with Back-drill VIPPO + Full VIPPO PCB configuration. Crosssection location indicated in Figure 4(b). Crack location in L2, L6 and L10 joint indicated by white arrows.

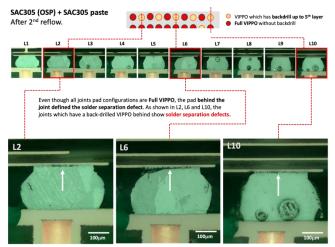

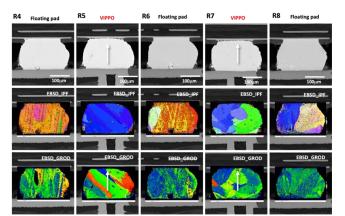

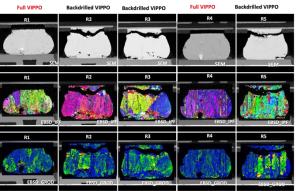

Unlike the SAC305 ball + SAC305 paste joint configuration, the hybrid LTS and full LTS solder joint configuration in Figure 5(b) and (c) do not show any open and defect signature during the second reflow. Given the fact that the reflow profile has a peak temperature of 185°C, which is lower than the temperature point where the disconnection occurred in SAC305, the solder separation defects did not occur for both, full LTS and hybrid LTS joint configurations. Figure 6 shows the full SAC305 solder joint sample cross section after the second reflow per back-drilled VIPPO + full VIPPO PCB and dog bone/floating pad configuration. The cross-section locations are indicated in Figure 4(b) and (c). As shown in the optical images in Figure 6(a), the solder joints which reveal a solder separation are all full VIPPO locations. They are located next to a back-drilled VIPPO. In Figure 7, solder separation defects are observed at the full VIPPO locations surrounded by the dog-bone/floating pad locations. The associated EBSD inverse pole figure (IPF) images revealed that the solder separated joints have larger grains (R5 and R7). Compared to the full VIPPO joints, the dog-bone / floating pad joints have smaller grains indicating strain induced sub-grain structure development (R4, R6, and R8). Since the solder separation defect developed during the heating cycle during reflow before the full melting of the joint occurred, this means that during the cooling cycle, the solidification of the solder joint happened without a strong connection at the package side interface, resulting in larger grains forming during solidification. In comparison, the joints on dog-bone/floating pads maintain the connection and experienced the constraints (tension and compression) during heating and cooling, resulting in a sub-grain structure development. Figure 8 presents the hybrid LTS solder joint cross sections from two different assembled components: after first reflow (as-assembled condition) and after second reflow, Figure 8(a) and (b) respectively. Unlike the SAC305 joints after second reflow in Figure 6, these joints do not reveal any solder separation defects in the joints.

**Figure 7.** SEM and EBSD images of Full SAC305 joint with dog-bone/Floating pad + Full VIPPO PCB configuration after second reflow. Cross-section location indicated in Figure 4(c). Crack location in R5 and R7 joint indicated by white arrows.

(b) Hybrid LTS (SAC305+Sn-Bi-Ag\_Backdrilled VIPPO + Full VIPPO) after Second Reflow

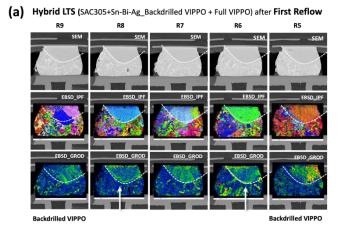

**Figure 8.** SEM and EBSD images of Hybrid LTS joints with Back-drilled VIPPO + Full VIPPO PCB configuration after first reflow (a) and second reflow (b). Cross-section location indicated in Figure 4(b). No crack or solder separation observed.

A larger grain structure can be observed after second reflow compared to the first reflow at the Sn-Bi eutectic region, which is the lower region of the solder joint near the PCB. The SAC305 region is mostly single or dual Sn grain structure. The EBSD grain reference orientation deviation (GROD) images per solder joint indicates the residual stress state [11]. In the first reflowed sample in Figure 8(a), the residual stress intensity shows a slightly higher stress inside the SAC305 region with a relatively higher intensity line at the interface between the Sn-Bi eutectic region and the SAC305 region, indicated with white arrows in R6 and R8 joints. Comparing the first reflow and the second reflow solder joints, the SAC305 region shows a decrease in residual stress after second reflow and no significant difference in residual stress were observed between back-drilled VIPPO and full VIPPO location joints.

**Figure 9.** Thermal cycling performance after first and second reflow on All Full VIPPO and Back-drilled VIPPO + Full VIPPO PCB configuration. (a)(b) Weibull distribution plot and (c)(d) failure cycle distribution plot. (a)(c) Full SAC305 joint configuration and (b)(d) Hybrid LTS configuration.

To identify any joint stability degradation per full VIPPO and Back-drilled VIPPO + full VIPPO configuration, thermal cycling was performed on as-assembled and second reflow applied components. Two solder joint configurations are selected: full SAC305 and hybrid LTS. The Weibull plot in Figure 9(a)(b) and the failure to cycle number distribution plot in Figure 9(c)(d) per full SAC305 and hybrid LTS presents the thermal cycling performance per condition. For full SAC305 in Figure 9(a) and (c), a small level of degradation is observed in second reflow components on full VIPPO configuration PCB, but a significant degradation is observed for second reflow applied components assembled on back-drilled VIPPO + full VIPPO configuration.

### (a)

Full SAC305, One reflow + thermal cycling, on Backdrilled VIPPO + Full VIPPO PCB

#### (b)

Full SAC305, Two reflow + thermal cycling, on Backdrilled VIPPO + Full VIPPO PCB

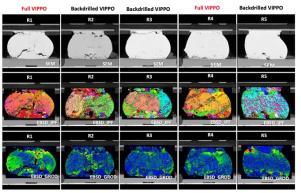

**Figure 10.** SEM and EBSD images of Full SAC305 joint with Back-drilled VIPPO + Full VIPPO PCB configuration after first reflow (a) and second reflow (b) then thermal cycled to failure.

The thermal cycle to failure numbers for the second reflow applied components are less than 5 cycles in most cases, which indicates that significant solder separation defect development already occurred in these components. Figure 10 shows the cross-section SEM and EBSD images per full SAC305 thermal cycle to failure solder joints after first and second reflow. Crack propagation path in one reflow then thermal cycled components (Figure 10(a)) show the usual crack propagation path mostly at the package side interface without a significant difference between back-drilled VIPPO and full VIPPO joints. But the second reflow applied component then followed by thermal cycling shown in Figure 10(b), revealed solder separations with wide open gaps at the package side interface in joints R1 and R4. Both joint locations are full VIPPO joints. The back-drilled VIPPO in the same row shows usual crack propagation in R2, R3, and R5. The cross section shows that the full VIPPO joints already have a full solder separation defect possibly in mechanical contact and electrical connection, but revealed the disconnect after only a few thermal cycles. Since the full VIPPO joints already lost the mechanical stability and connection, the adjacent back-drilled VIPPO joints experience a higher than usual shear load during thermal cycling, resulting in a fast crack propagation and a wider gap in thermal cycle induced crack development. Compared to the full SAC305 solder joints, the hybrid LTS joints thermal cycling performance shown in Figure 9(b) and (d) reveal a similar level of thermal cycling to failure cycle number distribution regardless of the full VIPPO and back-drilled VIPPO + full VIPPO configuration with first and second reflow conditions.

# CONCLUSION

Through a series of in-situ resistance measurement during second reflow, the accurate separation time and temperature are identified per design configuration and solder joint alloy material combination. The solder separation defect induced failures detected at 210-212°C at full VIPPO solder joint locations, which are adjacent to solder joints with higher zaxis expansion, in this case, back-drilled VIPPO and dogbone/floating pad locations. Three different solder alloys were selected to investigate the sensitivity to solder separation defects along with the evaluation per long-term thermal cycling performance. The results indicated that the separation defect in second reflowed SAC305 joints can be mitigated with using the SAC305+SnBiAg hybrid solder joint configuration and full LTS configuration since it has lower than 212°C assembly peak temperature. Thermal cycling performance after second reflow also shows the hybrid LTS is not affected by the uneven VIPPO distribution induced stress conditions. The presented study elaborates the parameters associated with the solder separation failure per board design configuration, and also provides the potential solution to mitigate the failure. An in-depth analysis on the solder joint microstructure utilizing Electron-backscattered diffraction (EBSD) supports the test results leading to the mechanism associated with the solder separation failure.

# ACKNOWLEDGEMENT

This work is an outcome of a collaboration project between Cisco CQT and SK Hynix. The authors thank Greg Baty in Portland State University CEMN for his support on the EBSD analytical work and MK Electron for the SAC305 and Sn-Bi-In solder spheres material support and ball attachment process.

# REFERENCES

- 1. Mei-Ling Wu and Jia-Shen Lan, Soldering & Surface Mount Technology, 29 (2), 75-84 (2017).

- B. Keser, R. Alvarado, A. Choi, M. Schwarz and S. Bezuk, Proceeding of IEEE 64<sup>th</sup> Electronic Components and Technology Conference (ECTC), Orlando, FL, 925-930 (2014).

- 3. Titus, B. Jaiswal and T. Dishongh, IEEE Transactions on Advanced Packaging, 27(4), 630-639 (2004).

- 4. M.Kelly, M.Jeanson, T.Younger, J.Bielick, T. Lewis, and M. Ferrill, Journal of SMT, vol 30(3), 28-36 (2017).

- J. Savic, M. Nagar, W. Xie, M. Ahmad, D. Senk, A. Bansal, N. Islam, P. Oh, R. Pendse, H. Choi, and S.Lee, Proceeding of IEEE 62<sup>nd</sup> Electronic Components and Technology conference, San Diego, CA, 450-456 (2012).

- 6. Steven Perng, Weidong Xie, Tae-Kyu Lee, and Cherif Guirguis, Proceedings of SMTA International, Rosemont, IL, 104-108 (2015).

- 7. Steven Perng and Weidong Xie, Transient Solder Separation of BGA Solder Joint During Second Reflow Cycle, IPC APEX EXPO, San Diego, conference presentation (2017)

- 8. M.Sheikh, A.Hsiao, W.Xie, S.Perng, and T.K.Lee, Localized Multi-axis Loading Impact on Interconnect Thermal Cycling Performance in Viain-Pad Plated Over (VIPPO) Board Configuration. *J. Electron. Mater.* **50**, 699–709 (2021).

- 9. JEDEC Standard, JESD22-A104D, Thermal Cycling, March (2009).

- Tae-Kyu Lee, Thomas Bieler, Choong-un Kim and Hongtao Ma, Fundamentals of Lead-Free Solder Interconnect Technology, Chapter 6, Springer, 169-210 (2015).

- 11. S.Wright, N.Nowell, and D.Field, Microscopy and Microanalysis, 17(3), 316 (2011).