# ELECTROPLATED COPPER FILLING OF THROUGH HOLES INFLUENCE OF HOLE GEOMETRY

Ron Blake, Andy Oh, Carmichael Gugliotti, Bill DeCesare, Don DeSalvo, Rich Bellemare MacDermid Enthone Electronics Solutions Waterbury, CT, USA Richard.bellemare@macdermidenthone.com

#### ABSTRACT

This paper discusses a through hole copper filling process for application in high density interconnect constructions on thin IC and LED substrates where high reliability and thermal management are essential. The process consists of a two step acid copper plating cycle. The first step utilizes periodic pulse reverse electroplating to form a conductive copper bridge across the middle of a through hole followed by direct current electroplating to fill the resultant vias formed in the bridge cycle.

The ability of the process to fill a variety of through hole sizes on substrates of varying thickness while minimizing the overall surface copper build up are critical in applications requiring efficient thermal management as circuit miniaturization continues.

The through hole fill technology and factors that affect its performance such as substrate thickness and through hole diameter will be presented in this paper.

Key words: PPR electroplating, via fill, thermal management, through hole fill

# INTRODUCTION

Resin or paste plugging of through holes in cores has been a part of build up technology, especially in IC substrate construction, for many years. Technological advances encompassing increased circuit density and stacked via construction coupled with higher power devices, have added an extra dimension of thermal management where a copper filled through hole becomes advantageous (See Figure 1).

Advantages of copper filled through holes include :

- Reduction in CTE mismatch of resin/paste plug

- Stable platform for stacking microvias

- Solid pillar structure within through hole

- Lower likelihood of adhesion failure on the plated over filled via

- High thermal conductivity of copper

New technologies were developed to completely fill through holes and vias in build-up core layers in HDI and IC substrates with solid copper. Among the approaches for filling through holes in a thin core board with copper was DC plating.

Figure 1. Paste Plugged Vias and Copper Filled Vias

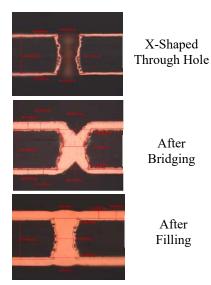

In this two stage technique, one begins with an X-shaped through hole. In the initial stage of plating, copper is preferentially deposited in the middle of the through holes until the growing copper deposits meet to form a bridge. The resulting double blind vias then fill to complete the copper filled through hole. Terms to describe this process are bridge and fill (See Figure 2).

Figure 2. Stages of DC Copper Filling

The use of a single copper plating solution in a single step is the ideal process for filling through holes with copper. For thin core materials of approximately 100um in thickness with through holes of 100um diameter at the outsides and 50-70um at the middle, a plated surface copper thickness of less than 25um can be expected.

DC copper plating for through hole filling is limited by the thickness of the substrate. As substrate thicknesses approach 200um, the propensity for the formation of cavities and inclusions increases as well as the necessity to plate much

higher thicknesses of surface copper. This is due to extended plating times necessary to completely fill the through hole (See Figure 3). This effect is exacerbated for boards with mechanically drilled, straight walled, through holes as the "dogboning" tendencies of electroplating will tend to close the openings of the through holes more quickly.

Figure 3. Cavity Defects and Surface Copper in Thicker Substrates

# BACKGROUND

#### **Two Step Through Hole Fill Technology**

In the two step through hole fill process, the bridging and filling steps are split into two separate steps utilizing two different plating solutions. The advantage is that each process can be optimized for its intended function. The combined process offers a much more robust bridge and fill system capable of filling a broader range of hole diameters and substrate thicknesses with copper while minimizing excessive plated surface copper.

The two step through hole fill technology begins with either mechanically or laser drilled through holes processed through primary metallization including plasma and/or permanganate desmear and made conductive either through electroless copper or the commonly available direct metallization processes such as graphite, carbon black, or organic polymer. A flash plate of copper can be used to ensure conductivity across the entire through hole wall.

The bridging of the center of the hole to form a double via utilizes a periodic pulse reverse copper plating system optimized to provide a cavity-free bridge with minimal surface copper. The filling of the resulting double vias utilizes via fill copper plating technology to provide accelerated filling of the vias while also minimizing surface copper.

# **Bridge Step using PPR Plating**

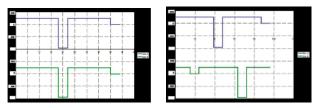

PPR plating is widely used for the conformal plating of high aspect ratio through holes. New rectifier designs and software now offer greater flexibility in developing complex waveforms that can provide plating results previously unobtainable. One of the features of newer rectifiers is the ability to impress asynchronous waveforms into a plating panel (See Figure 4).

Figure 4. Example of Synchronous and Asynchronous Waveforms

The use of asynchronous pulsed waveforms can accelerate the plating rate of the copper in the middle of the through hole up to 5 times that of conventional pulse waves (See Figure 5).

Figure 5. Example of Accelerated Plating at Hole Center

The electrolyte components of the bridge solution are typical of acid copper plating solutions: copper sulfate, sulfuric acid, chloride ion, and additives. The concentrations in this study are presented in Table 1.

#### Table 1. Bridge Bath Composition

| Component      | Concentration |

|----------------|---------------|

| Copper Sulfate | 240g/L        |

| Sulfuric Acid  | 110g/L        |

| Chloride Ion   | 85ppm         |

| Wetter         | 3%v/v         |

| Brightener     | 0.05%v/v      |

#### Filling Step using Via Fill Plating

Copper via filling technologies have been widely used in the manufacturing of HDI and IC packaging substrates. Copper via fill baths are DC plating systems that are specifically designed for filling vias. They provide preferential copper deposition within the via and inhibited deposition on the surface (See Figure 6).

This effect is accomplished by taking advantage of the difference in behavior of the additives in a via fill bath under different current density environments. The inside of the via is considered a low current density area versus the surface of the substrate. Suppressor additives in the via fill chemistry adsorb onto and inhibit copper deposition in high current density areas. The brightener additives adsorb onto and accelerate copper deposition in low current density areas.

At the beginning of the fill process where the current density differences between the bottom of the via and top are the greatest, the differential in deposition rate is greatest resulting in bottom up filling. As the via fills, this differential in deposition rate decreases until the via is near filled at which point the deposition rates in the via and on the general surface become equal due to the equalization of current densities. At this point, the copper deposits at an equal rate on both the surface and in the via.

# RESULTS

# **Bridge Optimization**

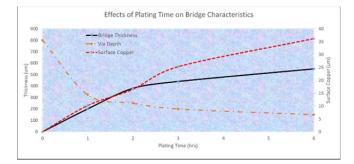

The results of the bridging cycle testing with respect to time are summarized in Figure 7.

Figure 6. Example of Accelerated Plating within Via

The electrolyte components of the via fill solution are typical of acid copper plating solutions: copper sulfate, sulfuric acid, chloride ion, and additives. The concentrations in this study are presented in Table 2.

| Table 2. Via I in Dath Composition |  |  |  |  |  |

|------------------------------------|--|--|--|--|--|

| Concentration                      |  |  |  |  |  |

| 200g/L                             |  |  |  |  |  |

| 100g/L                             |  |  |  |  |  |

| 75ppm                              |  |  |  |  |  |

| 0.9%v/v                            |  |  |  |  |  |

| 0.45%v/v                           |  |  |  |  |  |

| 0.8%v/v                            |  |  |  |  |  |

|                                    |  |  |  |  |  |

| Table 2. Via Fill Bath Co | omposition |

|---------------------------|------------|

|---------------------------|------------|

#### **EXPERIMENTAL**

One of the key steps in the through hole bridge and fill process is the determination of the bridge cycle to form a via with a shape and dimensions that is optimal for filling. Generally, a via of approximately 7 mils or less in diameter with an aspect ratio of approximately 0.75 - 1.0 is preferred for optimal filling. In this paper, a constant hole diameter and substrate thickness were used to illustrate bridge optimization with respect to time. Plating was done for various times and via depth, aspect ratio, surface copper, and bridge thickness were recorded.

Measurements of plated substrates of various thicknesses, hole diameters, and pitches were collected from various sources under optimized bridge and fill cycles. The data was analyzed to demonstrate the effect of hole size and panel thickness on the resulting deposits.

Figure 7. Bridge Characteristics vs Plating Time

The results showed that the bridge thickness increased quickly and linearly during the early stages of the process where the copper deposit extends outward from the center of the hole to close it and then begins to thicken and grow towards either side of the substrate surface. At a certain point, the thickness of the bridge levels out, increasing only slightly with time. The via depth decreased greatly in the early stages of plating and leveled out at a certain point. This occurred in the region where the bridge thickness also leveled out indicating that little further change in via dimensions can be expected after this point.

The plated surface copper increased steadily during the entire process. Minimization of plated surface copper from the bridge step is dependent upon the total plating time necessary to form an optimum via.

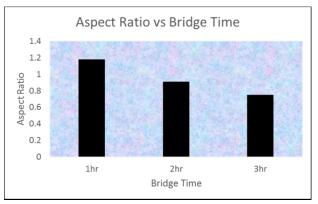

The change in the aspect ratio of the vias formed on either side of the plated copper bridge are presented in Figure 8.

Figure 8. Via Aspect Ratio vs Plating Time

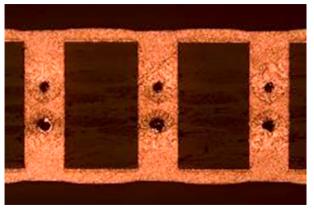

The results showed that the aspect ratio of the vias formed on either side of the bridge decreased with time. In this case, the desired aspect ratio of 0.75 was obtained in 3 hours for this particular hole size and substrate thickness. If the aspect ratio of the vias is too great, there will be a tendency to form cavities in the fill process as the tops of holes will close faster than the via can fill (See Figure 9). If the aspect ratios of the vias are too low or the diameters of the vias are too great, one will then get conformal plating due to the mechanism of differential current densities previously discussed.

Figure 9. Cavities in High Aspect Ratio Vias

# Effects of Hole Size and Substrate Thickness on Through Hole Fill Results

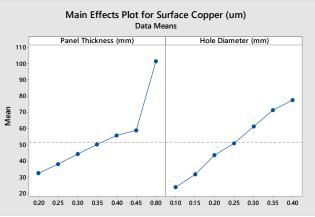

The data of surface copper as a function of through hole diameter and panel thickness is presented in Table 3. The main effects plots are presented in Figure 10. The total plated surface copper is the sum of the plating thickness from both the bridge and the via fill processes.

**Table 3.** Total Surface Copper vs Hole and PanelDimensions

| Hole            | Panel Thickness |                 |                |                 |                |                 |                |

|-----------------|-----------------|-----------------|----------------|-----------------|----------------|-----------------|----------------|

| Dia             | 0.2mm<br>8mil   | 0.25mm<br>10mil | 0.3mm<br>12mil | 0.35mm<br>14mil | 0.4mm<br>16mil | 0.45mm<br>18mil | 0.8mm<br>32mil |

| 0.1mm<br>4mil   | 20um            | 22um            | 24um           | 26um            | 28um           |                 |                |

| 0.15mm<br>6mil  | 25um            | 27um            | 30um           | 33um            | 36um           | 40um            |                |

| 0.2mm<br>8mil   | 30um            | 32um            | 36um           | 40um            | 44um           | 48um            | 75um           |

| 0.25mm<br>10mil | 35um            | 37um            | 42um           | 46um            | 50um           | 56um            | 90um           |

| 0.3mm<br>12mil  | 40um            | 44um            | 50um           | 56um            | 60um           | 70um            | 110um          |

| 0.35mm<br>14mil | 45um            | 50um            | 58um           | 65um            | 72um           | 80um            | 130um          |

| 0.4mm<br>16mil  |                 | 55um            | 70um           | 85um            | 100um          |                 |                |

| 0.45mm<br>18mil |                 |                 |                |                 |                |                 |                |

Figure 10. Main Effects Plot for Surface Copper

It is readily observed that hole diameter greatly affects the amount of total plated surface copper that can be expected for the through hole copper filling process. As the diameter of the through hole increases, the amount of surface copper that can be expected as a consequence of successfully meeting through hole filling requirements, increases. This is due to the fact that larger diameter holes require longer periods of time for the copper bridging process to extend across the diameter of the hole to close and form the vias and the longer periods of time to fully fill the resulting larger diameter vias. This can be substantial in the case of extremely wide holes.

It is also readily apparent that panel thickness greatly affects the amount of total surface copper for similar reasons. In the case of thicker panels, it requires more time for the bridge to build enough to provide vias of optimum aspect ratio. It logically follows that combining both large diameter holes with thicker substrates will result in more total plated surface copper than a thinner substrate with smaller diameter holes. This is illustrated in Figure 11. Plated surface copper for the thinner core material was 35um while the thicker core material was 93um.

Figure 11. Effect of Substrate Thickness on Surface Copper

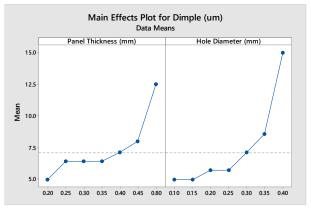

Another important characteristic of the copper plated through hole is the dimple size, especially if vias will be stacked or planarization is not desired. Figure 12 illustrates the main effects plots of hole diameter and panel thickness on dimple size.

Figure 12. Main Effects Plot for Dimple Size

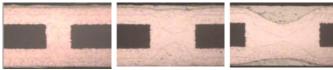

Dimple size, as with total copper surface plating, is greatly influenced by hole diameter and panel thickness. Dimple size increases greatly with holes greater than approximately 0.25mm in diameter and with panel thicknesses of greater that approximately 0.4mm in thickness. The increase in dimple size with hole diameter is due to the geometry of the vias formed in these larger holes after bridging. The larger diameter, lower aspect ratio holes will have more of a tendency to conformal plate due to the mechanisms of via fill previously discussed (See Figure 13).

Figure 13. Effect of Hole Diameter on Dimple Size

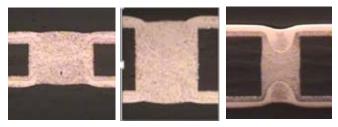

The increase in dimple size with panel thickness is due to the greater time in forming the bridge and getting an acceptable via while controlling the plated surface copper within reasonable limits. Figure 14 illustrates this effect on 0.35mm holes in 0.25, 0.40, and 0.80mm core materials where plating was stopped as the maximum allowed plated surface copper was reached.

**Figure 14.** Effect of Panel Thickness on Dimple Size (0.25, 0.40, and 0.80mm core)

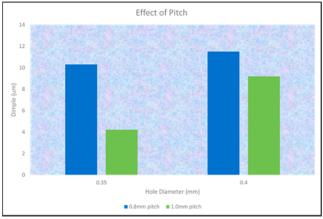

Limited work was done on the effect of the pitch of an array of holes on copper through hole filling in terms of dimple size. The results are summarized in Figure 15.

Figure 15. Effect of Hole Pitch on Dimple Size

The results indicated that, for a set hole diameter and panel thickness, the lower the pitch of the through holes (higher hole density), the larger the resulting dimple size. The reason for this phenomenon is that high density arrays can be considered high surface area features. As such, they will act as lower current density areas requiring longer times and/or higher current densities to meet minimum requirements versus isolated areas.

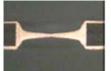

The physical properties of copper deposited in the copper through hole fill process are critical to the overall reliablility of the electronic device in which it is used. Typical properties for the combined deposit are presented in Table 4.

**Table 4.** Typical Properties of Copper Through Hole FillDeposit

| Plating cycle | Sample # | Plated copper<br>Thickness (mil) | Break Force<br>(lbf) | Weight (g) | Elongation (%) | Tensile Strength (PSI) |

|---------------|----------|----------------------------------|----------------------|------------|----------------|------------------------|

|               | 1        | 2.82                             | 62.75                | 0.9726     | 21.92          | 47098.0                |

| Copper plated | 2        | 3.23                             | 72.83                | 1.1146     | 21.19          | 47699.5                |

| with bridging | 3        | 2.71                             | 60.21                | 0.9348     | 20.79          | 47018.9                |

| plus via fill | 4        | 2.87                             | 62.89                | 0.9901     | 19.46          | 46368.8                |

| process       | 5        | 3.05                             | 68.12                | 1.0510     | 22.47          | 47314.6                |

|               | Mean     | 3.94                             | 65.36                | 1.0126     | 21.17          | 47100.0                |

# CONCLUSIONS

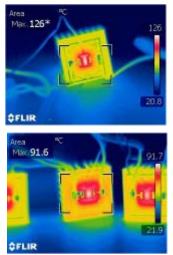

As technological advances continue in the electronics industry in the manufacturing of substrates for applications in HDI, IC, and LED, new challenges will arise for the engineers. With continued trends design toward miniaturization, new manufacturing techniques such as stacking of vias, and the use of high power devices that generate considerable heat, the need for improved methods of thermal management are required to efficiently conduct heat away from the electronic devices to improve device reliability and life. Copper through hole plating provides another tool to the engineer for the design of electronic circuitry. Figure 16 illustrates a real world application of copper through hole plating to conduct heat away from an LED device allowing it to operate at a lower temperature. In this example, the use of copper through hole filling reduced the operating tampeature of the device from 126C to 92C.

**Figure 16.** Use of Copper Through Hole Plating to Conduct Heat (Bottom Photograph)

The copper through plating process provides a versatile two step process consisting of a periodic pulse reverse step with specialized waveforms that allow the middle of a through hole to be bridged and sealed, forming two microvias that can subsequently be filled with DC based via fill chemistries.

The design engineer must understand the nuances of the copper through hole plating process and how the design of the board influences the results of each step of the plating

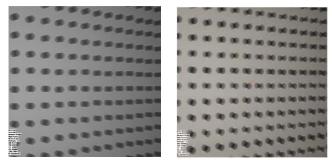

Figure 17. X-ray Imaging of Copper Through Hole Plating

process. The results presented in this paper illustrate the influence that board design features such as hole size and pitch and core thickness have on the critical outputs of the plating process such as ability to bridge, total plated surface copper, dimple size, aspect ratio, and total process time. When designing a substrate for the utilization of copper through hole plating, the design engineer must choose a suitable substrate and thickness and incorporate hole sizes and layouts that will minimize output variations. In this way, a robust, reliable copper through hole process can be realized (See Figure 17).