#### Integrated Electrical Test within the Production Line.

Michael Smith. Teradyne Inc. North Reading. MA.

#### **Abstract**

Many companies use "one stop testing" as a solution to the test issues in a manufacturing environment rather than discrete "islands of test". Low volume, high mix electronic manufactures are concerned about floor space, which can be expensive. As well as operator training, which can be considerable if a separate test solution is used for each product manufactured. Very high volume manufacturers can also benefit from a single stage electrical test solution if the test times are less than the beat rate of the line. This is especially true if the system in fully automated. As with low volume manufacturers floor space and operator training costs can be reduced, but the significant saving is in early defect detection that helps reduce scrap rates and improves line efficiency.

By combining electrical test into one system and having the system directly integrated into the production line, the system can detect defect at the earliest stage of the board manufacture. As a base, incircuit test (ICT) is a well-established electrical test technique and has been used successfully for a number of years and has a long history of being integrated into the production line. PXI has established itself as the standard for cost effective integrating of functional instruments into a test system. By combining ICT and PXI into one solution, it can perform incircuit test, help overcome ICT access issues and perform functional tests. This universal test solution provides a smaller footprint, consistent operator interface and overall a lower cost of test.

This paper will discuss the advantages of a universal integrated electrical test solution, at the normal Incircuit Test stage of production, to minimize production costs and help improve product quality using two case studies. One is a low volume high mix manufacturer and the other a high volume automotive electronics manufacturer.

#### Introduction

Incircuit test (ICT) is the established solution for electrical test in most electronic manufacturing environments integrated into the electronics production line. The advantage of using ICT is its ease of use, consistent and replicable results and minimum training required for different products that are being tested. The other forms of electrical test, found in the production environment are functional test and sometime system integrations test. Functional test is normally associated with the production line and tends to be product and company specific and unique, while system test tends to be after products have been finalized or assembled. Functional product test can sometime be extensive and therefore, multiple test stations may be required to service a single product. Functional test becomes remote from the production environment and therefore, when defects are detected, there is a delay in passing that information back to the production line and potentially many more similar defects can be produced. In a high mix environment there maybe many test stations at the end of the production line that are only used for short periods per day when the relevant product is being produce.

#### Development of computer controlled electrical test.

Manuel testing of products has been replaced in the last 40 years with computer controlled equipment. The first computer controller test systems were functional test units but these proved to be costly to program as devices became more complex. To overcome these issues then many electronic manufactures moved as many tests as possible to the controlled environment of the ICT system and to purpose built combinational test systems that can perform ICT and functional test but these tended to be expensive to program and run, with propriety hardware and software. As ICT became the standard for electrical test functional test solution had moved to general purpose hardware and software.

From the 1960's the General Purpose Instrument Bus (GPIB) or IEEE-488 instruments allowed for integration of instrument in to test systems including ICT systems but long wire lengths, synchronization issues and slow communications means this only had limited applications (GPIB based instruments today are slowly being replaced by LAN eXtensions for Instrumentation (LXI) which resolves some of the issues with GPIB).

Since 1987 test systems have begun to take advantage of integrated instruments such as the VME eXtensions for Instrumentation (VXI) bus that was developed from the VME standard for Motorola 68000. This allowed boards with four different form factors to be integrated into a system using a common VXI back plane. Simple instrument were designed to use the small A and B size boards (3U and 6U Eurocard format) while more complex boards, such as digital driver/sensors cards could use the C and D size boards. This type of instrumentation was popular with the Automatic Test Companies such

as GenRad and Teradyne who both developed testers using this standard in C and D size systems. The issues with this standard are that it is now seen as an old specification (1979), it was based on 16(32) bit and today it is still expensive compare to other instrument in other packages. To overcome some of the limitations of VXI the PCI eXtensions for Instrumentation (PXI) standard was introduced in 1997 based on standard PC buses structure to take advantage of the low cost associated with volume PC products. The boards used the Compact PCI board sizes which were equivalent to A and B size of boards available through the VXI standard with 3U (100mm x 160mm) and 6U. This has meant initially that complex instruments have tended to stay as VXI or GPIB as they require more space but with today's integration ability then we are seeing a great number of instrument available in PXI formats to take advantage of the small size, tight integration and lower costs.

#### Functional integration into ICT.

As one of the most prevalent instrument solution today, PXI is ideally suited to integrate into the ICT platform. PXI can provide tight software and hardware integration into exists architecture due to its size. (see Fig 1). By placing the instruments into existing instruments cages which normal sit directly under the Unit Under test (UUT) it can provide direct short wire connection for high performance measurements to maintain signal integrity(see Fig 2). It should also have a high performance switching matrix for distribution to key points on the UUT with access to the ICT system main analog bus for connection to the UUT through the ICT bed of nails fixture.

It is crucial that the functional instrument can be integrated with the ICT existing hardware. Not just the ability of the system to provide power for the UUT but also provide stimulus and measurement. The PXI instruments need to be fully synchronization with both analog and digital subsystems as today most UUT are hybrid with both digital and analog circuits. This enables complex digital vectors to be used and analog measurements made as well as analogy sources providing complex signals that can be "read" using digital sensor.

In develop test procedures than companies have their preferred solution that can be programs using National Instruments LabView or LabViews/CVI software, Microsoft Visual Studio or any other programming language. These solutions may already have been developed by engineering or manufacturing and should be transportable to the system without having to rewritten. In some cases a mixture of programming environments may have been used to take advantage of "best in class" for each application. Therefore it is essential that the ICT system with the functional PCI instrument can use as many different types of programming resources as possible.

#### Advantages of combined electrical test in low volume high mix manufacturer

There are a number of advantages in the integration of functional test into ICT test stage of a low volume high mix environment. .

#### Operator

High mix environments tend to use manual labor for loading and unloading UUT as it becomes too expensive to use automatic handlers that can switch to different products. By combines stations the first saving is in operators. If the integrated solution can replace two functional test stations then additional operators can be saved but normally only one operator is saved per shift. The ICT operator normally would need little additional training and therefore training cost are also reduced and this can be a substantial saving as training is normally required for each product in the high mix environment that needs a separate function test station. Having just one test stage also helped with the quality of products as reducing handling helps reduce damage due to handling and thus increases quality.

#### Fixture and Tooling.

Fixturing and tooling cost can also be saved with a combined ICT and functional test solution. The one fixture required by the integrated solution maybe slightly more expensive than the normal ICT fixture as it may need dual height probes for limited functional access but it would be less that the fixtures required by both the ICT and Functional test system. The fixture will also take up less storage space, require less handling and requires less maintenance than two fixtures combined, which would be multiplied out to a number of fixtures to deal with the multiple boards that would be produced on a high mix production line.

#### Overheads.

Using just one system helps reduces capital investment and allows for better utilization of production equipment inventory. Less power is needed for the test systems and the requirement for controlled environments such as air conditioning. Space

can be a crucial issue for high mix with a number of test systems needed for each board type that need to be close to the production area. ICT test times tend to be much shorter than typical beat rates in a high mix environment and therefore adding functional tests to ICT can also increase system utilization which also saves costs. Savings on calibration and servicing costs on all the function systems that are replaced plus reduced training for the first line response engineers that are normal required to fix any problems with the systems. ICT has been integrated into the factory MES/ERP systems for many years and by integrating the functional test into the common platform it can take advantage of the integration provided reducing the need to integrate and support a functional test station.

Diagnostic, Repair, Scrape and Final Quality

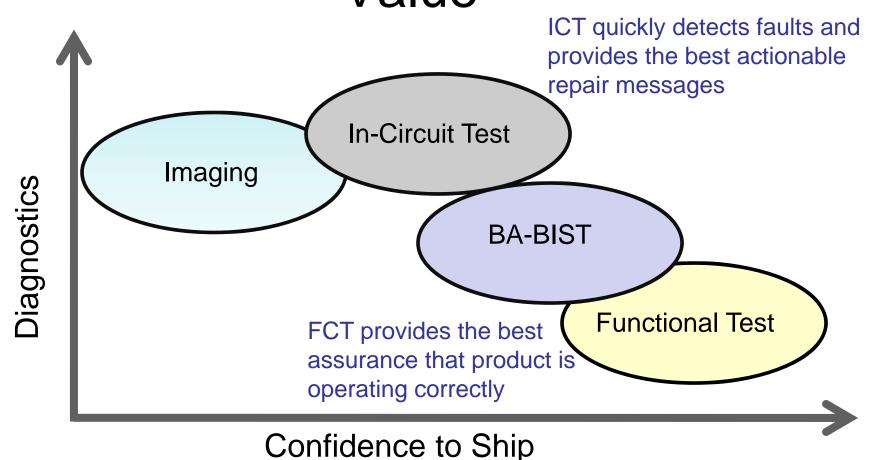

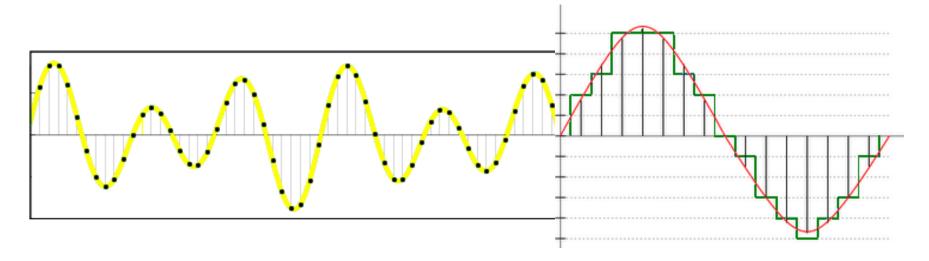

The DPMO model is the best way to analyze the advantage of combining ICT and functional into the same system for diagnostic, repair and scrap while making sure the quality remain constant. Tester capability can be defined (see Fig 3) for each inspection system. With the transfer of the tests from the standalone test system to the integrated solution then the defect coverage will remain the same. The advantages will come in diagnosis and repair due to lower costs of the standard look and feel of the ICT environment.

Using a DPMO cost model for a single board in a high mix low volume environment with the assumptions as seen in fig 4 than the estimated cost of separate ICT and Functional diagnostic and repair would be around \$20,000 (see Fig 5). By combining the two functions into one, it can be assumed that the diagnostic rate would be inline with the rate used for ICT and the time to verify and time to repair would drop closer to the expected ICT rates. Then the saving at just this stage can reduce the combined costs to around \$13,000 (see Fig 6) while keeping the final quality the same. These saving of around \$7,000 would then be repeats for all the products that were being produced using the integrated solution.

#### Advantages Of Combined Electrical Test In High Volume Automotive Electronics Manufacturer

There are a number of advantages in the integration of functional test into ICT test stage for a high volume automotive environment.

Automatic Board Handling.

The high volume automotive would normally be fully automated with handling systems on both ICT systems and any functional test systems in the production line. By combining functional test into ICT than the cost of the functional system, the board handler and diagnostic loop convey costs can be saved. In a normal environment this would be around \$75K per functional test cell.

Fixture and tooling.

As with low volume there is still a saving in fixturing and tooling costs. The handler fixture required by the integrated solution maybe slightly more expensive than the normal ICT fixture but it would be less that the fixtures required by both the ICT and Functional test system. Typically the fixture used in a handling system is better suited for the combination of both ICT and functional test as it has more control over the board height within the fixture. This control allows different high probes to be used for selective access to the UUT that maybe required for functional or boundary scan testing. Again this type of fixture would require less maintenance than having to maintain two or more fixtures.

#### Overheads.

Overhead savings are similar to the high mix low volumes but with a few differences. As with the other example having just one system reduces capital investment and allows for better used of production equipment inventory and less power is needed for the test and handling systems. Again saving on calibration and servicing costs of the functional system as well as training for the first line response engineers. With a test cell removed from the production line the overall reliability is improved by the reduction in handling. Integrating the functional test into ICT also allows the tests to be closer to the production equipment and take advantage of the integration that is normal with an ICT machine into the production line manufacturing execution system (MES). The ICT system provides the integration and the MES system can be used to identify production problems much earlier in the process than an end of line functional solution.

Diagnostic, Repair, Scrape and Final Quality.

Using the DPMO model with the same Tester capability (see Fig 3) for each inspection system as the high mix example then we get the following results.

Using the cost model for a typical high volume automotive board with the assumptions as seen in fig 7 than the estimated diagnostic, repair and scrape cost of separate ICT and Functional test would be around \$12M (see Fig 8). By combining the two functions into one and using the same saving assumptions used for the previous model, then the saving at just this stage can reduce the combined costs to around \$9.5M (see Fig 9) which is a saving of \$2.5M while still keeping the final quality levels.

#### Conclusion

With tight integration then combining ICT with functional test to perform electrical test in the production line does reduced fixture and tooling costs, lower handling costs, reduced development costs, requires fewer test operators, allows faster production beat rate, and greater system utilization. The standard DPMO model is also a good method of determining operational cost savings from the diagnostic, repair and scrap area which are on top of the capital cost savings and reduction in labor costs. Combining electrical test leads to a reduction in the overall cost of test and thus manufacturing costs.

#### References.

More information can be found on the following web sites on the follow topics:-

PXI specifications 1) http://www.pxisa.org 2) http://www.picmg.org PICMG specifications **IEEE** specifications 3) http://www.ieee.org PCI specifications 4) http://www.pcisig.com VME specification 5) http://www.vita.com VXI specifications 6) http://www.vxi.org VISA specifications 7) http://www.vxipnp.org

8) http://www.lxistandard.org LXI specification

9) http://zone.ni.com/devzone/cda/tut/p/id/3419

History of GPIB(IEEE-488)

#### Definitions.

PCI Peripheral Component Interconnect PXI PCI eXtensions for Instrumentation

**VME** Versa Module European

VME eXtensions for Instrumentation VXI

LAN Local Area Network

LAN eXtensions for Instrumentation. LXI

ICT Incircuit Test UUT Unit Under Test

**GPIB** General Purpose Instrument Bus

The Institute of Electrical and Electronics Engineers **IEEE**

DPMO Defects per Million Opportunities MES Manufacturing Execution System

# Integrated Electrical Test within the Production Line

Michael Smith

Teradyne Inc

North Reading. MA

### Content

- Electrical test techniques and comparisons

- Available instrumentation standards

- Advantages of using PXI for functional test integration

- DPMO ROI Calculator for estimating manufacturing costs

- Low Volume / High Mix case analysis

- Automated High Volume case analysis

- Conclusion

# Main Electrical Test Techniques used in the Production Line

### **In-Circuit Test**

- Simple test generation

- Good fault coverage

- Fast throughput

- Excellent diagnostics

- Complex test fixtures

- Standard test equipment

### Functional / System Test

- Complex test generation

- Variable fault coverage

- Longer test times

- Ambiguous diagnostics

- Simpler test fixtures

- Customized instruments

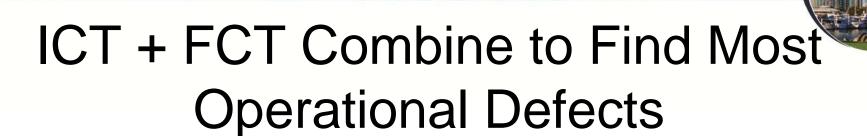

# Both ICT & Functional Test Add Value

(iNEMI: PCOLA / SOQ / FAM)

5015 CAN

# Typical Multi-Stage Electrical Test

### In-Circuit

Full access to nets

Detect Shorts/Opens

Verify each component

PLD Programming

Automated execution

Excellent diagnostics

### **Functional**

Limited access to nets

Detect Operation defects

Verify critical functions

Slower test times

Manual execution

Multiple stations

### **System**

Assembled product

Detect System defects

Verify mission operation

Slowest test times

Manual execution

Load final firmware

Multiple stations

# Instrument Standards Enabling Functional Test

IEEE-488 General Purpose Instrument Bus (GPIB)

- •Approved in 1975

- •Slow communication speeds

### VME Extensions for Instrumentation (VXI)

- Established in 1987

- Architecture based on VMEbus standard

- Expensive compared to other options

### LAN Extensions for Instrumentation (LXI)

- •LXI Consortium established in 2004

- Based on Ethernet standards

- Good replacement for GPIB

### PCI Extensions for Instrumentation (PXI)

- •Introduced in 1997

- Based on low cost PC standards

- Smaller instrument sizes

# Advantages of PXI Solutions

- Based on industry standard PC architecture

- Communicates using PCI bus

- Volume of PC based test solutions lowers instrument costs.

- Large number of instruments available

- Compact PCI instrument form factor

- 3U instruments are just 100mm x 160mm

- Support for software programming standards

- National Instruments LabVIEW

- Microsoft Visual Studio

PXI's small size, low cost, and use of "Window standards" makes it ideal for integration into ICT test systems

## PXI Expansion Board for ICT

- Plugs directly into ICT Backplane

- Does **not** expand tester footprint

- Communicates with the PC Controller using the standard PCI instrument bus

- Supports 2 PXI

Expansion Boards

and up to 8 PXI

instruments

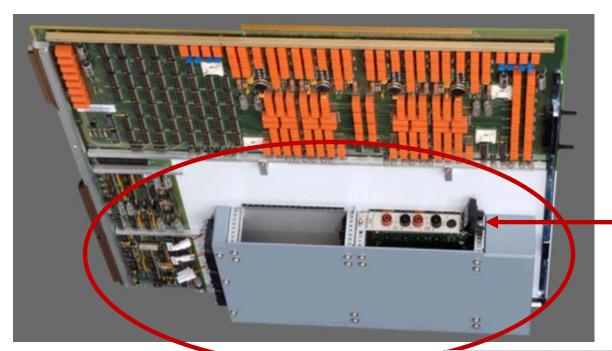

# Tight Integration with ICT System

The PXI Expansion Board plugs directly into the ICT Backplane along with the standard ICT instruments

## **PXI Expansion Bottom Board**

Compliant with PXI Specification Rev 2.2

PXI Instrument Chassis

Supports 43U size PXIInstruments

This example shows one instrument plugged into the

■ PXI chassis

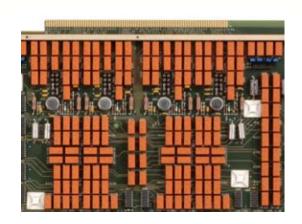

# PXI Expansion Top Board

- Flexible Signal Distribution Hub

- Direct short wire connections for critical signals

- High performance switching matrix to select receiver locations

- Access to ICT main analog bus allows signals to be scanned to any location on the test fixture

- Access to the tester's IEEE-488

(GPIB) instrument bus

- AC and DC Buffers

Custom designed for ICT System

# Integrated PXI/ICT Instruments

- The PXI Expansion Board can be fully synchronized with both the ICT analog and digital subsystems.

- This enables programmers to create complex analog, digital, and coherent mixed signal tests that use a combination of PXI and ICT instruments

# Advantages of Integration

- There are a number of cost advantages in the integration of functional test into ICT test

- Operator savings

- Lower fixture / tooling costs

- Reduced board handling

- Reduced test overhead

- Re-use of test procedures

- Reduction of test stages

- Better test equipment utilization

- Improved diagnostics, faster repair, reduced scrap and better product quality

# **Operator Savings**

- High mix environments tend to use manual labor for loading and unloading UUT

- Expensive to use automatic handlers due to switching costs

- Custom Functional test stages are difficult to automate

- Often they are not part of in-line production flow

- Combining test cells can reduce labor costs

- The ICT operator needs little additional training

- Eliminating test stages generally improves product quality

- Reducing operator handling

- Less variables

# Lower Fixture/Tooling Costs

- Goal is to eliminate functional test fixture and have single electrical test fixture

- Fixture may require more complexity

- Dual height probes for limited access during functional tests

- More expensive than ICT fixture but less expensive than cost of creating independent test fixtures

- Combined fixture requires less storage space

- Overall fixture and tooling costs should be lower with combined test solution

# Overhead Savings

- Reduction in functional test stations

- Better utilization of production equipment

- Less idle time for ICT system

- Reduction in equipment floor space

- Saving on system calibration and servicing

- Less power for the test and handling systems

- Reduced effort integrating with factory Manufacturing Execution System (MES)

- Defects identified earlier in the production process

## Case 1 Analysis: Low Volume / High Mix Manufacturer

## Case Assumptions

- Low volume / high mix production line

- Separate ICT and Functional electrical test stages

- Separate operators for each test stage

- Image inspection is part of manufacturing process

- Standard test capability and effectiveness as published by iNEMI

### **Product Statistics**

- 2000 solder joints

- 400 components

- 1500 boards per year

- \$100 value per board

- 2400 opportunities for error

- Board DPMO = 375

# **Equipment Capability Matrix**

|                           | Imaging | ICT | Functional | System |

|---------------------------|---------|-----|------------|--------|

| Test Access               | 99%     | 90% | 70%        | 80%    |

| Structural Fault Coverage | 50%     | 95% | 90%        | 60%    |

| Electrical Fault Coverage | 0%      | 85% | 95%        | 99%    |

| Structural Test Coverage  | 50%     | 86% | 63%        | 48%    |

| Electrical Test Coverage  | 0%      | 77% | 67%        | 79%    |

| Effective Test Coverage   | 41%     | 84% | 64%        | 53%    |

| False Fail Rate (ppm)     | 500     | 50  | 5          | 2      |

- Each technique offers different test coverage and false fail rates

- Early test stages detect assembly process defects best

- Later test stages detect operational defects best

Source: iNEMI 2000

### iNEMI ROI Calculator

| Repair Assumptions                           |         |      |         |         |            |          |

|----------------------------------------------|---------|------|---------|---------|------------|----------|

| Repair Yield                                 | 85%     | [%]  |         |         |            |          |

| # of Repair Cycles Permitted                 | 5       |      |         |         |            |          |

| Scrap Rate                                   | 0.0076% |      |         |         |            |          |

| Defect Rate Assumptions (Process Capability) |         |      |         |         |            |          |

| Electrical DPMO                              | 250     | [ppm | ıC]     |         |            |          |

| Structural DPMO                              | 400     | [ppm | ıJ]     |         |            |          |

| # of Structural Defects/Board                | 0.8     |      |         |         |            |          |

| # of Electrical Defects/Board                | 0.1     |      |         |         |            |          |

| Debug/Diagnosis and Repair Costs             |         |      | Imaging | ICT     | Functional | System   |

| Hourly Labor Cost of Verification/Diagnosis  |         | [\$] | \$65    | \$65    | \$85       | \$85     |

| Hourly Labor Cost of Repair                  |         | [\$] | \$50    | \$50    | \$50       | \$50     |

| Time to Verifcation / Diagnose One Defect    |         | [min | 1       | 5       | 60         | 120      |

| Time to Repair One Defect                    |         | [min | 15      | 15      | 30         | 60       |

| Cost to Debug/Diagnose One Defect            |         | [\$] | \$1.08  | \$5.42  | \$85.00    | \$170.00 |

| Cost to Repair One Defect                    |         | [\$] | \$12.50 | \$12.50 | \$25.00    | \$50.00  |

| ReTest Cost                                  |         | [\$] | \$0.50  | \$0.50  | \$1.00     | \$2.00   |

#### Combining ICT & FT labor has positive economic effects

- Diagnostic hourly rate reduced from \$85 to \$65

- Time to diagnose one defect reduced from 60min to 10min

- Time to repair one defect reduced from 30min to 15min

- Retest cost reduced from \$1.00 to \$0.50

### iNEMI Calculator Results

|                                            | Imaging | ICT      | Functional | System      |          |

|--------------------------------------------|---------|----------|------------|-------------|----------|

| Structural Defects Before Test [per board] | 0.8     | 0.404    | 0.05858    | 0.0216746   |          |

| Structural Defects After Test [per board]  | 0.404   | 0.05858  | 0.0216746  | 0.011270792 |          |

| Electrical Defects Before Test [per board] | 0.1     | 0.1      | 0.0235     | 0.0078725   |          |

| Electrical Defects After Test [per board]  | 0.1     | 0.0235   | 0.0078725  | 0.00163748  |          |

| Structural Defects Found [per board]       | 0.3960  | 0.3454   | 0.0369     | 0.0104      |          |

| Electrical Defects Found [per board]       | 0.0000  | 0.0765   | 0.0156     | 0.0062      |          |

| Total Defects Found [per board]            | 0.3960  | 0.4219   | 0.0525     | 0.0166      |          |

| First Pass Yield                           | 67.3%   | 65.6%    | 94.9%      | 98.3%       |          |

| Overall Test Effectiveness                 | 44%     | 84%      | 64%        | 56%         |          |

| DPMO Remaining on Board after Test         | 210.0   | 34.2     | 12.3       | 5.4         | Total    |

| Annual Cost of Verifying                   | \$644   | \$3,428  | \$6,698    | \$4,243     | \$15,012 |

| Annual Cost of Repair                      | \$7,425 | \$7,911  | \$1,970    | \$1,248     | \$18,554 |

| Annual Cost of Scrap                       | \$18    | \$6      | \$1        | \$0         | \$25     |

| Annual Cost of Retest                      | \$245   | \$258    | \$77       | \$50        | \$630    |

| Total Cost of Test                         | \$8,087 | \$11,345 | \$8,669    | \$5,491     | \$34,221 |

| Total Cost of Test              |               | \$8,087 | \$11,345 | \$1,839   | \$5,491     | \$27,354 |

|---------------------------------|---------------|---------|----------|-----------|-------------|----------|

| Annual Cost of Retest           |               | \$245   | \$258    | \$38      | \$50        | \$59     |

| Annual Cost of Scrap            |               | \$18    | \$6      | \$1       | \$0         | \$2      |

| Annual Cost of Repair           |               | \$7,425 | \$7,911  | \$985     | \$1,248     | \$17,569 |

| Annual Cost of Verifying        |               | \$644   | \$3,428  | \$854     | \$4,243     | \$9,168  |

| DPMO Remaining on Board aft     | er Test       | 210.0   | 34.2     | 12.3      | 5.4         | Total    |

| Overall Test Effectiveness      |               | 44%     | 84%      | 64%       | 56%         |          |

| First Pass Yield                |               | 67.3%   | 65.6%    | 94.9%     | 98.3%       |          |

| Total Defects Found [per boar   | d]            | 0.3960  | 0.4219   | 0.0525    | 0.0166      |          |

| Electrical Defects Found [per t | ooard]        | 0.0000  | 0.0765   | 0.0156    | 0.0062      |          |

| Structural Defects Found [per   | board]        | 0.3960  | 0.3454   | 0.0369    | 0.0104      |          |

| Electrical Defects After Test [ | er board]     | 0.1     | 0.0235   | 0.0078725 | 0.00163748  |          |

| Electrical Defects Before Test  | [per board]   | 0.1     | 0.1      | 0.0235    | 0.0078725   |          |

| Structural Defects After Test   | per board]    | 0.404   | 0.05858  | 0.0216746 | 0.011270792 |          |

| Structural Defects Before Tes   | t [per board] | 0.8     | 0.404    | 0.05858   | 0.0216746   |          |

|                                 |               | Imaging | ICT      | ICT FT    | System      |          |

- results in average cost savings of \$7K/yr to produce 1500 boards

- Calculator uses iNEMI standard DPMO cost model

- Savings achieved by finding defects sooner, repairing them faster, using typical ICT operator

# Case 2 Analysis: High Volume Automotive Manufacturer

# Overhead Savings for this Case

- Elimination of functional test station conveyor

- Estimate \$75K less in handler equipment

- Reduced production floor space

- Savings depend on facility cost per square foot

- Less expensive fixture kits

- Press Down pneumatics on automated ICT systems support lower cost cassette type fixture kits with greater control for testing with dual height probes

## Case Assumptions

- High volume automated production line

- Separate ICT and Functional electrical test stages

- Image inspection is part of manufacturing process

- Standard test capability and effectiveness as published by iNEMI

### **Product Statistics**

- 4000 solder joints

- 1000 components

- 250000 boards per year

- \$200 value per board

- 5000 opportunities for error

- Board DPMO = 370

| Repair Assumptions                           |         |        |         |         |         |          |

|----------------------------------------------|---------|--------|---------|---------|---------|----------|

| Repair Yield                                 | 85%     | [%]    |         |         |         |          |

| # of Repair Cycles Permitted                 | 5       |        |         |         |         |          |

| Scrap Rate                                   | 0.0076% |        |         |         |         |          |

| Defect Rate Assumptions (Process Capability) |         |        |         |         |         |          |

| Electrical DPMO                              | 250     | [ppmC] |         |         |         |          |

| Structural DPMO                              | 400     | [ppmJ] |         |         |         |          |

| # of Structural Defects/Board                | 1.6     |        |         |         |         |          |

| # of Electrical Defects/Board                | 0.25    | )      |         |         |         |          |

| Debug/Diagnosis and Repair Costs             |         |        | Imaging | ICT     | FT      | System   |

| Hourly Labor Cost of Verification/Diagnosis  |         | [\$]   | \$65    | \$65    | \$85    | \$85     |

| Hourly Labor Cost of Repair                  |         | [\$]   | \$50    | \$50    | \$50    | \$50     |

| Time to Verification / Diagnose One Defect   | •       | [min]  | 1       | 5       | 60      | 120      |

| Time to Repair One Defect                    |         | [min]  | 15      | 15      | 30      | 60       |

| Cost to Debug/Diagnose One Defect            |         | [\$]   | \$1.08  | \$5.42  | \$85.00 | \$170.00 |

| Cost to Repair One Defect                    |         | [\$]   | \$12.50 | \$12.50 | \$25.00 | \$50.00  |

| ReTest Cost                                  |         | [\$]   | \$0.50  | \$0.50  | 61.00   | \$2.00   |

#### Combining ICT & FT labor has positive economic effects

- Diagnostic hourly rate reduced from \$85 to \$65

- Time to diagnose one defect reduced from 60min to 10min

- Time to repair one defect reduced from 30min to 15min

- Retest cost reduced from \$1.00 to \$0.50

### iNEMI Calculator Results

| Test Strategy                              |             |             |             |             |              |

|--------------------------------------------|-------------|-------------|-------------|-------------|--------------|

|                                            | Imaging     | ICT         | FT          | System      |              |

| Structural Defects Before Test [per board] | 1.6         | 0.808       | 0.11716     | 0.0433492   |              |

| Structural Defects After Test [per board]  | 0.808       | 0.11716     | 0.0433492   | 0.022541584 |              |

| Electrical Defects Before Test [per board] | 0.25        | 0.25        | 0.05875     | 0.01968125  |              |

| Electrical Defects After Test [per board]  | 0.25        | 0.05875     | 0.01968125  | 0.0040937   |              |

| Structural Defects Found [per board]       | 0.7920      | 0.6908      | 0.0738      | 0.0208      |              |

| Electrical Defects Found [per board]       | 0.0000      | 0.1913      | 0.0391      | 0.0156      |              |

| Total Defects Found [per board]            | 0.7920      | 0.8821      | 0.1129      | 0.0364      |              |

| First Pass Yield                           | 45.3%       | 41.4%       | 89.3%       | 96.4%       |              |

| Overall Test Effectiveness                 | 43%         | 83%         | 64%         | 58%         |              |

| DPMO Remaining on Board after Test         | 211.6       | 35.2        | 12.6        | 5.3         | Total        |

| Annual Cost of Verifying                   | \$214,500   | \$1,194,497 | \$2,398,690 | \$1,546,795 | \$5,354,482  |

| Annual Cost of Repair                      | \$2,475,000 | \$2,756,531 | \$705,497   | \$454,940   | \$6,391,968  |

| Annual Cost of Scrap                       | \$12,499    | \$4,298     | \$524       | \$176       | \$17,497     |

| Annual Cost of Retest                      | \$68,383    | \$73,260    | \$26,685    | \$17,870    | \$186,199    |

| Total Cost of Test                         | \$2,701,999 | \$3,955,327 | \$3,104,711 | \$2,001,910 | \$11,950,146 |

|                               |                | Imaging     | ICT         | ICT FT     | System      |             |

|-------------------------------|----------------|-------------|-------------|------------|-------------|-------------|

| Structural Defects Before Te  | st [per board] | 1.6         | 0.808       | 0.11716    | 0.0433492   |             |

| Structural Defects After Test | [per board]    | 0.808       | 0.11716     | 0.0433492  | 0.022541584 |             |

| Electrical Defects Before Tes | t [per board]  | 0.25        | 0.25        | 0.05875    | 0.01968125  |             |

| Electrical Defects After Test | [per board]    | 0.25        | 0.05875     | 0.01968125 | 0.0040937   |             |

| Structural Defects Found [pe  | r board]       | 0.7920      | 0.6908      | 0.0738     | 0.0208      |             |

| Electrical Defects Found [per | board]         | 0.0000      | 0.1913      | 0.0391     | 0.0156      |             |

| Total Defects Found [per boa  | rd]            | 0.7920      | 0.8821      | 0.1129     | 0.0364      |             |

| First Pass Yield              |                | 45.3%       | 41.4%       | 89.3%      | 96.4%       |             |

| Overall Test Effectiveness    |                | 43%         | 83%         | 64%        | 58%         |             |

| DPMO Remaining on Board at    | fter Test      | 211.6       | 35.2        | 12.6       | 5.3         | Total       |

| Annual Cost of Verifying      |                | \$214,500   | \$1,194,497 | \$152,858  | \$1,546,795 | \$3,108,649 |

| Annual Cost of Repair         |                | \$2,475,000 | \$2,756,531 | \$352,749  | \$454,940   | \$6,039,219 |

| Annual Cost of Scrap          |                | \$12,499    | \$4,298     | \$1,378    | \$176       | \$18,352    |

| Annual Cost of Retest         |                | \$68,383    | \$73,260    | \$13,343   | \$17,870    | \$172,856   |

| Total Cost of Test            |                | \$2,701,999 | \$3,955,327 | \$506,984  | \$2,001,910 | \$9,339,077 |

- Combining ICT & FCT results in average cost savings of \$2.5M/yr to produce 250000 boards

- Same or better quality than separate test stages

- Savings achieved by finding defects sooner and repairing them faster

### Conclusion

- Integrating functional test with ICT can have significant benefits

- Reduced fixture and tooling costs,

- Lower handling costs,

- Reduced development costs,

- Fewer test operators,

- Faster production beat rate

- Greater system utilization

- PXI's small size, low cost, and use of "Window standards" makes it ideal for integration into ICT test systems

- The iNEMI DPMO ROI calculator can be used to predict diagnostics, repair and scrap cost savings for different production scenarios