# INNOVATIVE CU ELECTROPLATING PROCESS FOR ANY LAYER VIA FILL WITH PLANER VIA TOP AND THIN SURFACE COPPER

Saminda Dharmarathna<sup>a</sup>, Todd Clark<sup>a</sup>, William Bowerman<sup>a</sup>, Kesheng Feng<sup>a</sup>, Jim Watkowski<sup>a</sup> <sup>a</sup>MacDermid Enthone,

CT, USA

Saminda.dharmarathna@macdermid.com

## ABSTRACT

Revolutionary new consumer electronic products and their miniaturization drives capitalization on the latest technologies available to increase the functionality of PCBs. High density interconnect (HDI) technology is one of the fastest growing in printed circuit board industry. This technology allow us to utilize the PCB real estate more efficiently by including laser microvias, fine lines and high performance thin materials. The increased density enables more functions per unit area. Advanced HDI technology have multilayer PCBs with copper filled stacked microvias. These Advanced HDI PCBs could house more complex interconnect structures. These very complex structures provide the necessary connection pathways for modern day large pin-count chips.

Microvias play crucial role in HDI designs, mechanical or laser drilling of blind micro vias (BMV's) and successive filling has become the standard manufacturing technique. Specially, small microvias laser drilling is the only possible way to achieve quality via geometry. A typical laser drilled microvia has a diameter of typically 150,125, or 100  $\mu$ m. Which are optically aligned and with a pad diameter typically 300, 250 or 200 $\mu$ m, providing added routing density and reliable solder attachment. Most common arrangement of these microvias are via-in-pad, offset, staggered or stacked.

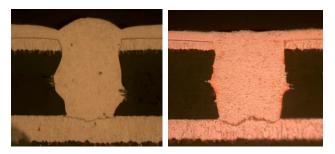

**Figure 1.** (a) Filled via having momentum bump, (b) advanced via fill having planer via top after filling.

When processing multilayer PCB boards specially with stacked vias it is essential to have a planer via top after microvia fill. Vias with bumps as shown in Figure 1(a) will cause issues in bonding the next layer, and most importantly the bumps will interfere with the laser drilling of the next stocked via layer and cause the next layer to have uneven via geometry Due to these disadvantages, PCB manufacturers need another additional processing step to chemically etch the

deposit until they reach a planer surface to build the next layer without issues.

Here we discuss an innovative DC acid copper via fill formulation, for VCP (Vertical Continues Plating) applications. A flat top can be obtained after the viafill, no additional processing is necessary to planarize the surface such as chemical or mechanical polishing. Excellent filling was obtained with thin Cu on the surface ~ 10  $\mu$ m when controlled within the given parameters. Process optimization thermal and physical characterization was also reported.

Key words: Copper electroplating, Via Fill, PCB metallization.

### **INTRODUCTION**

Progress of the Printed Circuit Board (PCB) industry over the last few decades has pushed PCB architecture to the limits. In order to please the modern-day electronics industry, it is essential to use unconventional board designs. Continuous efforts are being taken to make the electronic devises lighter, smaller, and faster. As the technology evolves there are more opportunities and means to add more components to the circuit board thereby achieving above mentioned qualities for electronics. High-density interconnects (HDI) technology, a relatively young but well utilized technology where, densification of functionality on PCBs using the same or less amount of area is possible. [1] For instance, by having sequential build up (SBU) of microvias, modern PCBs can accommodate more surface mount components in less area. Since the popularity of HDI technology grew rapidly among PCB design communities, innovative and reliable via filling solutions are necessary for multilayer PCB processing. One of the challenge with the sequential build up process is that the features of preceding laver such as bumps on the vias cause problems while processing the subsequent layer. While laser drilling, beam can be scattered by a dome shaped via top and make the drilling difficult and cause consequent via to have an unusual shape. Thus, the via shape, especially the walls show abnormalities, and these abnormalities grow progressively with additional layer. Chemical etching is used in the industry when the via top is not flat, however

that add more processing cost and generate more waste. Therefore, having a flat via top after filling without chemical reduction is essential. Such process will be cost effective, have high yield and have less environmental impact that ones with chemical reduction. Here we introduce two processes to fill different sizes of vias with flat via top after filling.

No chemical reduction is necessary after filling to get a planer via top. These processes are free from formaldehyde a carcinogen being pushed out of plating industry especially in Europe as a safety measure. Thus, these processes have lot of advantages over conventional via fill and are ideal for any layer viafill with multilayer processing.

### Acid Copper Via Fill

Electrodepositions is the one of the crucial steps in developing a circuit board, this is where all the current routing network is plated on to the PCB board through traces, vias and throw holes. Copper is the choice of conductive metal due to several advantages such as cost and relatively high electrical conductivity. Therefore, usage of cu as an electroplating metal has grown immensely over the last few decades along with the methods of plating the metal. Advanced, proprietary board designs require cutting edge plating tools and innovative solutions. As a result, within last few decades impingement plating tools became a widespread tool among plating industry. Here we present two solutions to fill vias.

Copper via filling baths typically have high concentrations of Copper (up to 250 g/L Copper sulfate) and lower concentrations of acid (approximately 50 g/L sulfuric acid) to promote rapid filling. Organic additive are used to control the plating rate and obtain acceptable physical properties. These additives must be designed carefully to tailor the customer needs such as size of the vias need to filled, yield, surface Cu thickness, Cu distribution tolerance throughout the panel and the shape of the via after plating. Typical systems will contain carriers, brighteners, and levelers. In theory, it is possible to fill vias only with carrier and Brightener. However, there are practical issues with two component systems like, larger dimple size, conformal fill, and difficulty analyzing.

Both carrier and leveler act as suppressors but in different ways and can be classified as different types of suppressors. Type I suppressors like carriers can be deactivated by the brightener whereas type II suppressors like levelers do not undergo deactivation. Carriers are typically high molecular weight polyoxyalkyl compounds. [2] Typically, they get adsorbed on the surface of the cathode and form a thin layer by interacting with chloride ions. Consequently, carrier reduces the plating rate by increasing the effective thickness of the diffusion layer. [3] Consequently, the energy level over the cathode surface topography is being equalized (same number of electrons locally for plating at any cathode surface spot) so that the resultant deposit becomes more uniform and evenly distributed.

On the other hand, brighteners increase the plating rate by reducing the suppression. They are typically small molecular weight Sulfur containing compounds, also called grain refiners.

Levelers typically consists of nitrogen bearing linear/branched polymers, heterocyclic or nonheterocyclic aromatic compounds being typically quaternized (positively charged). These compounds will adsorb selectively on high current density sites such as edges and corners, local protrusions and prevent copper over plating in high current density areas. [4]

Tests were completed in 8-liter cell, Figure 2 and 200-liter pilot tanks. Insoluble anodes were used for higher applicable current densities, easy maintenance and a uniform copper surface distribution. Each bath was made up, dummy plated for 1 Ah/L, analyzed, adjusted to correct additive levels, and then the test panel was plated. Each test panel went through a pre-clean cycle of 1 min acid cleaner, 1 min rinse, 1 min 10% sulfuric acid before the plating.

Figure 2. Test cell 8 L with educator flow and knife agitation.

# **Conditions and bath Components**

Table 1 shows the operational conditions and optimum additive levels. Typically, via fill baths have high copper and low acid to achieve the desired bottom up fill.

Table 1. Bath components and plating conditions.

| Parameter                                              | Process I<br>Process I |         | Process II     |          |

|--------------------------------------------------------|------------------------|---------|----------------|----------|

| i aranicici                                            | Range                  | Optimum | Range          | Optimum  |

| Wetter                                                 | 5 - 8 mL/L             | 7 mL/L  | 9 - 25 mL/L    | 10 mL/L  |

| Brightener                                             | 0.75 - 1.2 mL/L        | 1 mL/L  | 0.5 - 1.5 mL/L | 1 mL/L   |

| Leveler                                                | 3– 6 mL/L              | 4 mL/L  | 0.5-2.5 mL/L   | 1.5 mL/L |

| Copper Sulfate (CuSO <sub>4</sub> .5 H <sub>2</sub> O) | 190 -220 g/L           | 200 g/L | 230 - 250 g/L  | 240 g/L  |

| Sulfuric Acid Electronic Grade                         | 40 - 60 g/L            | 50 g/L  | 55 - 65 g/L    | 60g/L    |

| Chloride Ion (Cl <sup>-</sup> )                        | 40 – 60 ppm            | 50 ppm  | 40 – 60 ppm    | 50 ppm   |

### Via Fill Mechanism

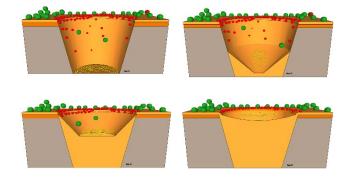

The control of the growth rate inside and outside the via is controlled by the additives. Figure 3 shows a schematic representation of via growth. Different role played by each additive is shown. Even though the adsorption is exaggerated and shown as highly localized, both selective and non-selective adsorption occur during plating. Additive compositions must be controlled in a set range shown in table 1 in order to get the desired "bottom-up filling". Analytical tools such as Cyclic Voltammetry Striping (CVS) analysis, and Hull cell plating is the most common in the industry, may be utilized.

According to Figure 3, suppressor is shown green, leveler with red and brightener with yellow. Wetter molecules mainly adsorbed on the surface suppressing the surface, while the leveler adsorb selectively on to the negatively charged areas, due to the positively charged quaternized N group. This prevents over plating at the edges and avoids premature closure of the via leaving voids in the center of the via. Brightener being a small Sulfur containing molecule diffuses faster into the via and accelerates the plating. During the plating process, the geometry of the via changes continuously the brightener become concentrated inside the via causing a rapid plating in the via. This is called the curvature-enhancedaccelerator coverage (CEAC) mechanism. [5] Finally, when the via gets leveled with the surface and the plating rates inside the via and on the surface become equal, the bottom up filling stops. However, depending on how strong the additive adsorbs and desorb the brightener may not diffuse as expected and the high concentration of the brightener will keep accelerate the plating and the momentum will over plate the via resulting in a "momentum pump" shown in Figure 1(A).

Figure 3. Schematic representation of bottom-up filling

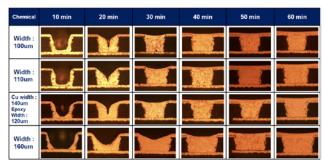

In order to understand the mechanism of the filling, the plating was stopped at every 10 minutes and cross sectioned. Figure 4 shows the results for 3 different via sizes. All three vias were filled within 40 min at 1.2 ASD, and flat via top was obtained after the filling. Most importantly as explained before bottom up filling occurred, which gives a void free fill. Both process I and II showed similar filling mechanism.

Figure 4. Via filling progression over 60 minutes for different vias

### Effect of inorganic components

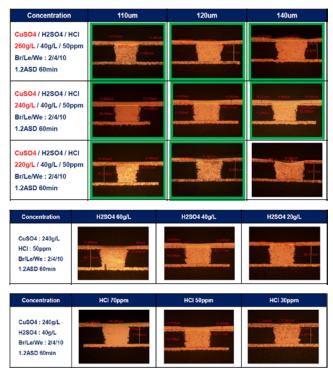

The effect of inorganic components that is, CuSO4, Sulfuric acid, and chloride ion were studied by varying the concentrations. CuSO4 concentration was tested from 220 - 260 g/L, sulfuric acid from 20 - 60 g/L, and Cl-from 30 - 70 ppm. Platings done with process I is shown in Figure 5.

**Figure 5.** Effect of Inorganic components CuSO4, Sulfuric acid, and chloride ion

Three via sizes were considered for the effect of CuSO4 110, 120, and 140 um. In which 140 um via showed difference in filling, for high CuSO4 at 260 g/L even though 110 and 120 um via did not show much difference in filling, 140 um showed bump after filling. This is due to the momentum bumping phenomena, with high Cu the effect is exaggerated. Lower CuSO4, at 220 g/L cause a larger dimple for 140 um via. The best filling with flat via top was obtained when the CuSO4 was at 240 g/L. Both Sulfuric acid and Chloride had little to no effect on the concentration range tested. Which shows the process has a large tolerance for acid and chloride.

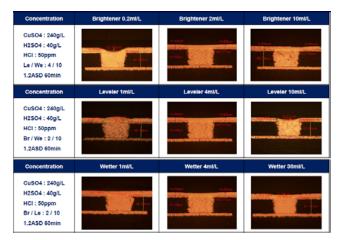

**Figure 6.** Effect of organic components Wetter, Brightener, and Leveler.

Next the effect of organic additives on plating was studied by changing the concentration of additives. Brightener concentration was changed from 0.2 to 10 mL/L, Leveler from 1 to 10 mL/L and wetter from 1 to 30 mL/L. Lower Br concentration gave a larger dimple, this could be due to lack of acceleration at the crucial part of bottom up filling. Nevertheless, the Br operating window was extended up to 10 mL/L without having any adverse effects on the filling. Optimum concentration of the leveler was 4 mL/L, planer via top was obtained after filling. However, at lower Leveler at 1 mL/L momentum bump was observed after filling, this could be due to lack of suppression due to low Leveler. On the other hand, at high Leveler concentration caused a dimple this is due to the non-selective adsorption of leveler at high concentration.

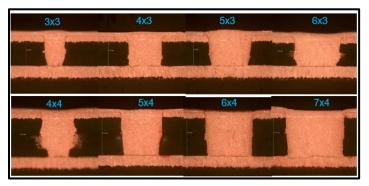

Figure 7. Filling peformance of Process II

| 0.4 LPM | 0.6 LPM | 0.8 LPM | 1.2 LPM |

|---------|---------|---------|---------|

|         |         |         | X       |

Figure 8. Effect of flow rate on fill.

Mass transport, is one of the most important factor has a significant impact on microvia fill. Figure 7 shows the filling performance as a function of solution flow for different via sizes. The results show that lower levels of current density provide better microvia filling performance. However, this improvement comes at the price of increased risk of improper fill in deeper vias such as  $100\mu$ m. This may lead to defects such as "seams" and cavities within the filled via. Therefore, solution flow must be carefully controlled to achieve the best filling performance.

CRYSTAL STRUCTURE AND PHYSICAL PROPERTIES

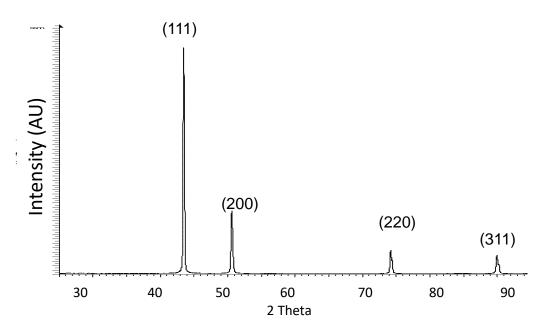

Figure 9. Typical X-Ray Diffraction pattern of the electroplated deposit.

X-Ray diffraction was used to understand and compare the crystal structure with the known standard. Typical diffraction pattern was obtained as the standard reported in the literature, figure **9** with reflections from planes (111), (200), (220), and (311) were observed. Narrow sharp peaks in the XRD pattern indicates highly ordered Cu crystals in the deposit.

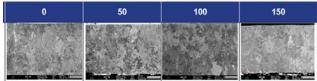

Table 2. Grain structure with bath age

Table 2 summarizes the grain structure as a function on bath age. Evaluation was done at four different bath ages, 0, 50, 100, and 150 Ah/L. After the bath reach the certain age a plating was done and grain structure evaluation was performed using ion milling technique in all cases fine equiaxial grain structure was seen. No significant change in the grain structure was observed as the bath age.

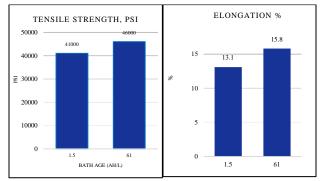

Figure 10. Physical properties of process II at different bath age.

$$\begin{aligned} \text{Mean average cross sectional area (in2)} \\ &= \frac{Weight of the sample (lbs)}{Length of tensile sample (in)x density of copper (g/in3)} \dots Eq 1 \\ \end{aligned}$$

$$\begin{aligned} \text{Tensile Strength} &= \frac{Maximum load (lbs)}{Mean cross sectional area (in2)} \dots Eq 2 \\ \end{aligned}$$

$$\begin{aligned} \text{Elongation} &= \frac{(Length at break - Original gage length)}{Original gage length} \times 100\% \dots Eq 3 \end{aligned}$$

Two most important physical properties to the PCB manufacturing are tensile strength and elongation %, these properties show the tolerance of the deposit for thermal stress. The Cu deposit plated with additives suppressor, grain refiner, and leveler will show characteristic physical properties.

Tensile strength and elongation were measured according to the IPC TM-650, 2.4.18.1 standards. A stainless-steel panel was plated with the current formulation. Sample strips were extracted from the plated panel and baked in an oven at 125°C for four to six hours—An Instron instrument was used to test the strips. The measurements were used to calculate tensile strength and elongation % using equations 1, 2, and 3. Figure 10 shows the results at two different bath ages, fresh bath and bath age around 62 Ah/L. According to the results properties improved with the bath age.

### CONCLUSION

Here we present processes for acid copper via fill applications for any layer via fill. Formulations showed excellent via fill capability, with minimum surface Cu and most importantly gave a planer via top after filling the via. Evaluation of structure showed stable crystal structure during aging. The physical properties, tensile strength and elongation improved as the bath aged. All the additive components can be analyzed with Cyclic Voltammetry Stripping analysis.

### REFERENCES

D62-D67 (2015)

[1] Clyde F. Coombs Jr., Printed Circuit Handbook, Sixth edition, McGraw-Hill, New York, 2008.

[2]P.Broekman. A.Fluegel, C.Emnet. C.Roeger-M.Arnold. Goepfert, A.Wagner, N.T.M.Hai, D.Mayer, Classification of suppressor additives based on synergistic and antagonistic ensemble effects. Electrochimica Acta, Volume 56, Issue 13, 1 May 2011, Pages 4724-4734 [3] K. B. Herbert; S. Adhikari; J. E. Houser, Journal of the Electrochemical Society, 152 (5) C324-C329, 2005. [4] S. Dharmarathna et. al. High Throw DC Acid Copper Formulation for Vertical Continuous Electroplating Processes. IPC APEX Expo 2017, San Diego, California, February 14-16, 2017. [5] Y. Zhang, G. Ding, P. Cheng, H. Wang, Numerical Simulation and Experimental Verification of Additive Distribution in Through-Silicon Via during Copper Filling Process, Journal of The Electrochemical Society, 162 (1)