### **Assembly Challenges of Bottom Terminated Components**

Jennifer Nguyen, David Geiger, and Dongkai Shangguan, Ph.D. Flextronics International 1007 Gibraltar Drive Milpitas, CA, USA

### Abstract

Bottom terminated component (BTC) assembly has rapidly increased in recent years. This type of package is attractive due to its low cost and good functional performance (improved signal speeds and good thermal performance). However, it creates many challenges to the assembly process and post assembly inspection.

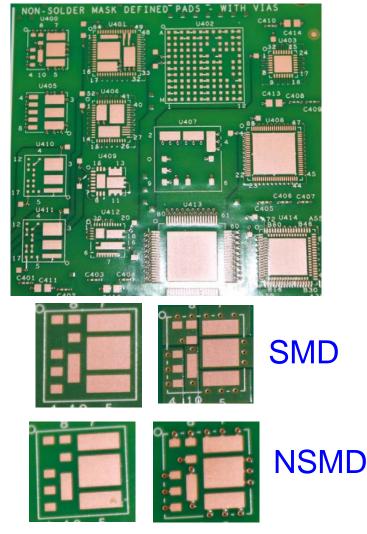

This paper discusses the design, assembly process and inspection challenges of bottom terminated components. The study considers many factors, including design variables (solder mask defined pad, non solder mask defined pad, mixed pad design, different via design, thermal connection, orientation, etc.), process variables (stencil design, reflow profile, reflow atmosphere, etc.), board surface finish variables (OSP, I-Ag, ENIG) and fabrication variables (solder mask thickness and type).

Keywords: bottom terminated component (BTC), quad flat no lead (QFN) package, land grid array (LGA) package, micro lead-frame (MLF) package, void, solder, SMT, lead-free.

### Introduction

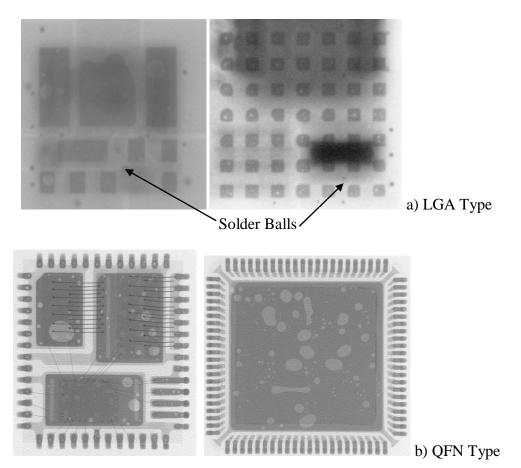

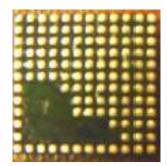

Bottom terminated components are leadless components for which terminations are protectively plated and are on the underside of the package [1]. They are all slightly different and have different names, such as QFN (quad flat no lead), DFN (dual flat no lead), LGA (land grid array), MLF (micro lead-frame), etc. BTC components are available in different sizes, lead counts, and designs. Most parts are unique from particular suppliers with unique pad designs.

BTC is relatively low cost and is attractive for volume applications. It is typically light and thin, ideal for handheld devices and consumer products. In addition, BTC has good electrical performance and excellent thermal dissipation. As a leadless device, it has low resistance and capacitance. The thermal pad is directly connected to the printed circuit board (PCB) and provides excellent heat transfer. However, there are many concerns and challenges on the assembly of BTC.

### **BTC Challenges**

### Design Uniqueness and Variation

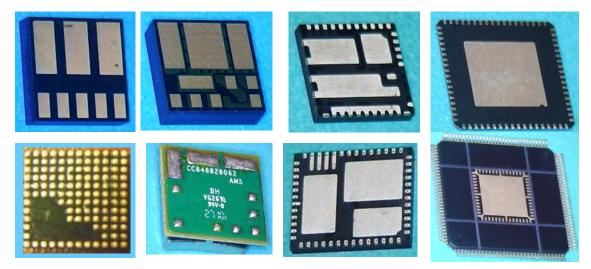

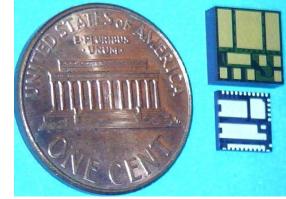

Most BTC components are unique from supplier to supplier and have their own pad design. There is no standardization on the component pitch, pad dimension, pad size and shape. Various BTC component pad designs are shown in Figure 1.

Figure 1 – Some BTC Package Designs

### Assembly Concerns

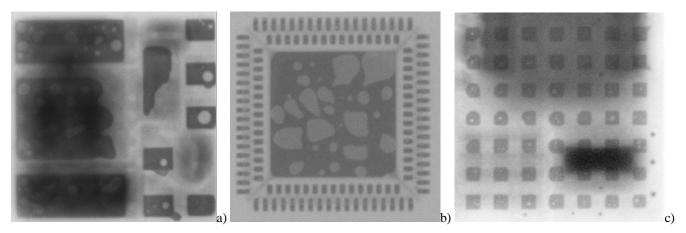

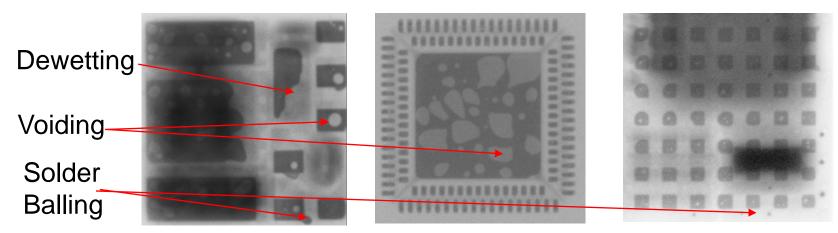

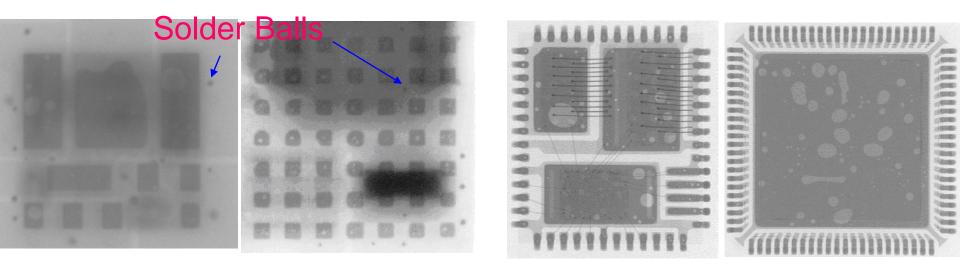

Assembly of BTC components requires appropriate stencil design and tight paste printing process control. A correct amount of solder is critical for having good solder joint quality and reliability. Too much solder paste may cause the component to bridge, tilt or float, but too little of solder can cause open or voiding defects. Voiding is the most concern for BTC components. BTC component typically has large thermal pad and provides no standoff. As a result, the flux volatiles cannot escape causing void formation during the reflow process [2]. Examples of BTC solder joint defects are shown in Figure 2.

Figure 2 - a) Pad Dewetting, Voiding, Solder Balling; b) Voiding; c) Voiding and Solder Balling

#### Inspection Challenge

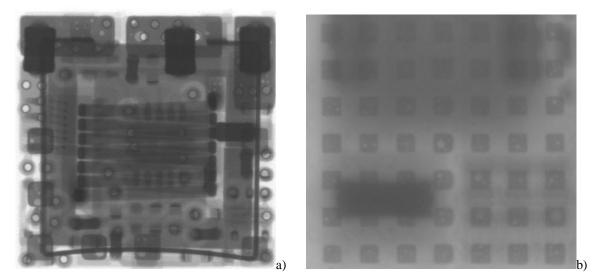

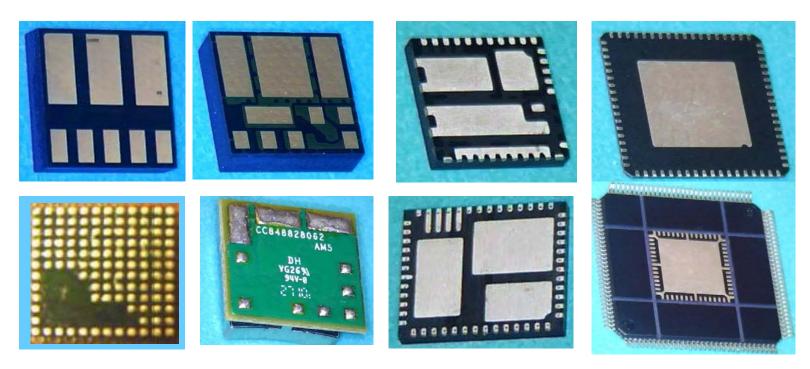

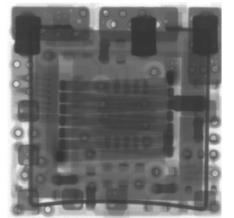

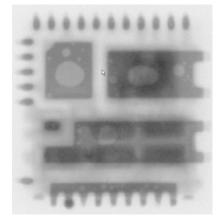

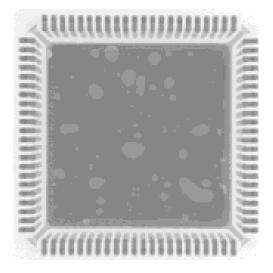

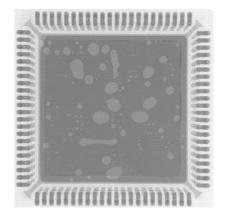

The solder joint of BTC components cannot be visually inspected. X ray inspection is required. Most x-ray equipment cannot inspect these components automatically. While some x-ray equipment can perform the inspection automatically, its accuracy is a concern. Since most BTC packages have an exposed die attach pad feature[1], it creates even more challenge for inspection than BGAs. The solder joint can be shadowed by the die attach pad or other components inside the BTC component. This results in unclear x-ray image and inaccurate voiding data (Figure 3). In some cases, multiple algorithms or programs are used to inspect one package (Figure 4). Some process issues such as solder balling and dewetting can escape from the automatic inspection program and have to be manually inspected. Besides, there is no industry standard on the voiding criteria for the large thermal pad of the BTC packages. X-ray inspection of BTC components can be time consuming for program generation and validation of the data.

Figure 3 – The leads of the BTC packages are shadowed by the die or other components inside the package. a) 2D Xray image of a LGA component shows that its leads are shadowed by other features in the component; b) 3D x-ray image of a different LGA package shows that many leads are shadowed and may result in inaccurate data.

As originally published in the IPC APEX EXPO Proceedings.

Figure 4 - a) Two different algorithms are needed in the program for x-ray inspection of this typical QFN package, one is for the outside signal leads (highlighted in yellow), and the other one is for the central thermal pad (highlighted in red). b) This QFN package has different pad designs, and multiple algorithms must be used for voiding data.

b)

#### Voiding and Reliability

Voiding is always seen on the BTC packages, mostly at the large thermal pads (Figure 2 and Figure 4). In some cases, the voiding percentage exceeds 25% (which is the criterion for inspection of BGA solder joints per IPC specifications). There are no industry criteria for acceptable voiding amount on BTC components. There is also lack of published data that correlates the impact of voiding on the thermal performance and solder joint reliability for BTC components. The solder interconnect reliability of BTC components depends on package design, pad design and size, and the assembly process (solder paste volume, standard off height, voiding), etc.

#### Cleanliness

BTC component has a low standoff height, making it difficult to clean the flux residues under the package using the water soluble process. For example, it is very difficult to clean QFN or LGA components with pitch below 0.5 mm; this could cause concerns related to dendritic growth and leakage. Thus, optimized cleaning process or the "right" solder paste material should be used for the assembly of these devices. No clean material is typically recommended. The power and signal pins should be separated (not adjacent to each other) in the design.

#### **BTC Test Vehicle**

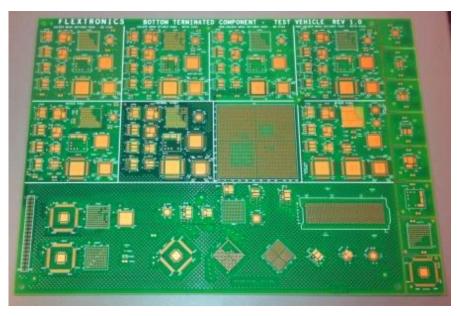

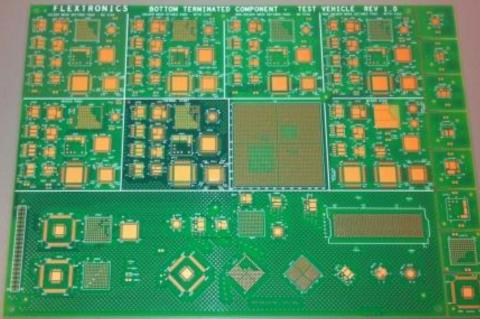

A test vehicle was designed by Flextronics for an internal study on PCB assembly of BTC components. Thirteen different BTC packages from various suppliers were included along with common packages (such as BGAs and chip components) (Figure 5). On this double-sided test vehicle with a dimension of 203mmX 280mm x 2.4mm (8"x11"x0.093"), many variables were included, such as: different pad designs (solder mask defined pad, non solder mask defined pad, mixed pad

design), different via designs, different thermal connection options, different orientations, different spacings, etc. The test vehicle also contains daisy chained BTC components for reliability study. Multiple board thicknesses (2.4mm and 3.2mm) and board surface finishes (OSP, I-Ag, ENIG) were included in the study. Different solder mask thicknesses and solder mask types were also investigated.

Figure 5 – Flextronics Bottom Terminated Component Test Vehicle, Rev 1

#### **Results and Discussions**

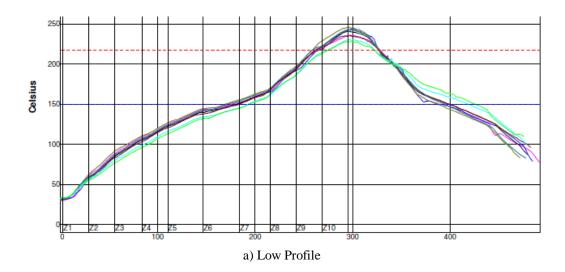

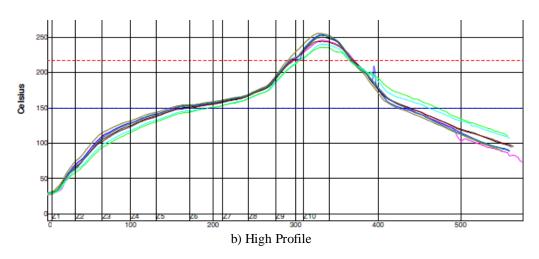

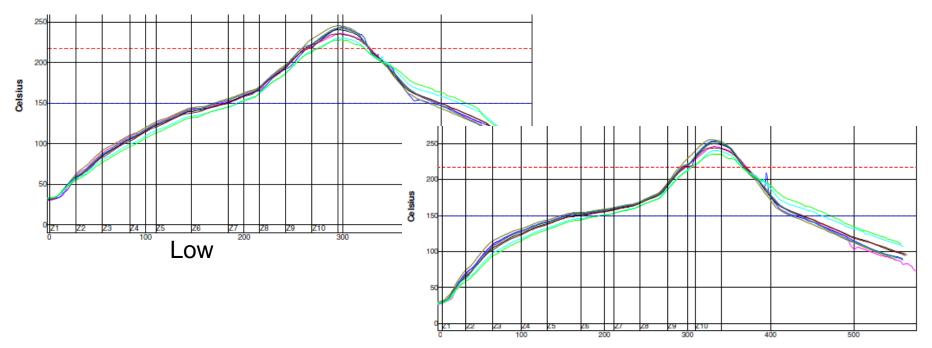

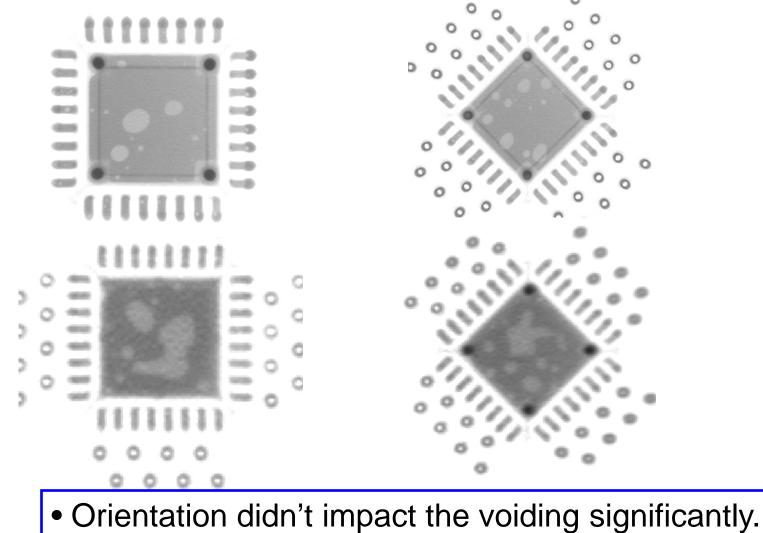

Multiple design of experiments (DOEs) were performed to study the impact of design, assembly process, fabrication variables and board surface finishes on the solder joint quality, especially on voiding and solder balling defects. Lead-free solder paste (SAC305) was used. In the first DOE, two different reflow profiles were tested (Figure 6). The boards were reflowed in both nitrogen and air atmosphere. It showed that the reflow profiles and reflow atmosphere did not have a significant effect on the BTC solder joint voiding (Figure 7). It was observed that voiding slightly increased with temperature. Nitrogen environment did not help to reduce voiding. In some cases, nitrogen reflow resulted in fewer but larger voids. Component orientation did not impact voiding slightly (Figure 8).

As originally published in the IPC APEX EXPO Proceedings.

|               | Low Profile |            | Hot Profile |           |

|---------------|-------------|------------|-------------|-----------|

| Locations     | Soak Time   | Peak Temp. | Soak Time   | Peak Temp |

| U100 (IP2004) | 85.75       | 236.06     | 140.54      | 245.93    |

| U309 (IP3837) | 82.48       | 243.9      | 139.69      | 253.56    |

| U703 (QFN32)  | 88.53       | 245.67     | 141.01      | 255.61    |

| U607 (DC-DC)  | 81.36       | 240.54     | 133.68      | 249.94    |

| U502 (LGA118) | 80.78       | 235.34     | 122.65      | 244.28    |

| U907(BGA196)  | 86.07       | 242.73     | 136.99      | 252.38    |

c) Profile Comparison

Figure 6 – Low and High Reflow Profiles

Figure 7 - Profile didn't impact voiding significantly. a) low profile, reflowed in air b) high profile, reflowed in air c) high profile, reflowed in N2

Figure 8 – Impact of orientation on voiding.

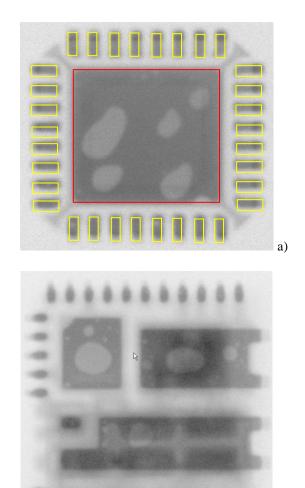

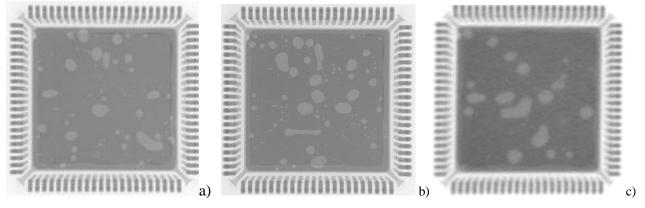

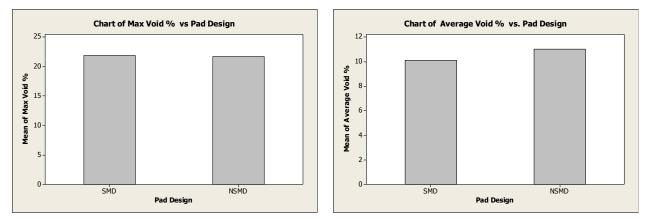

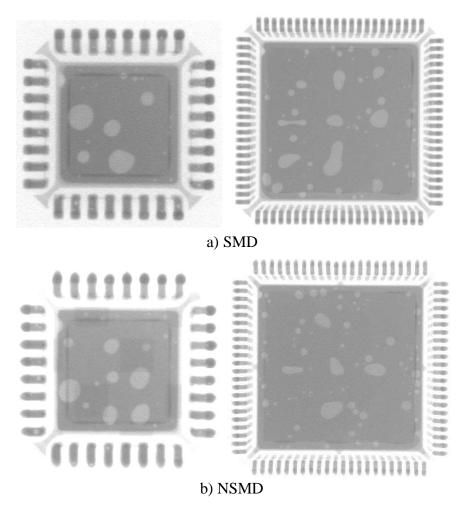

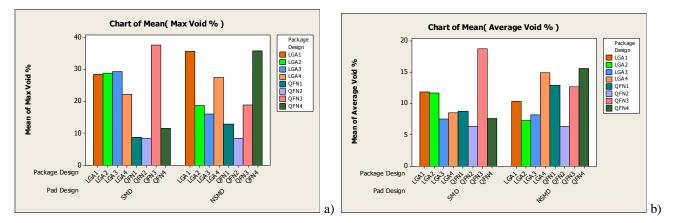

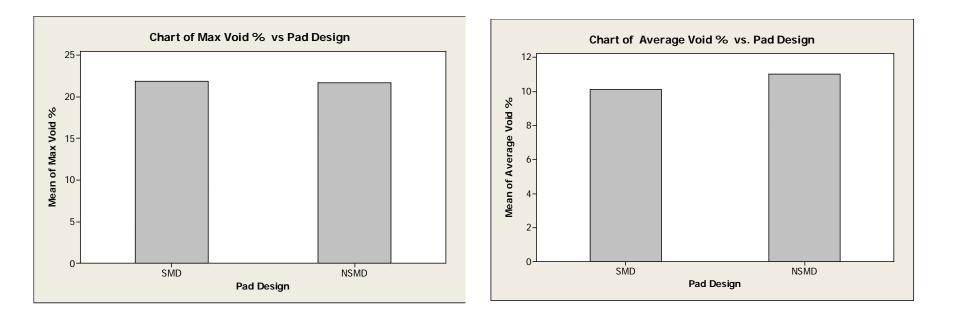

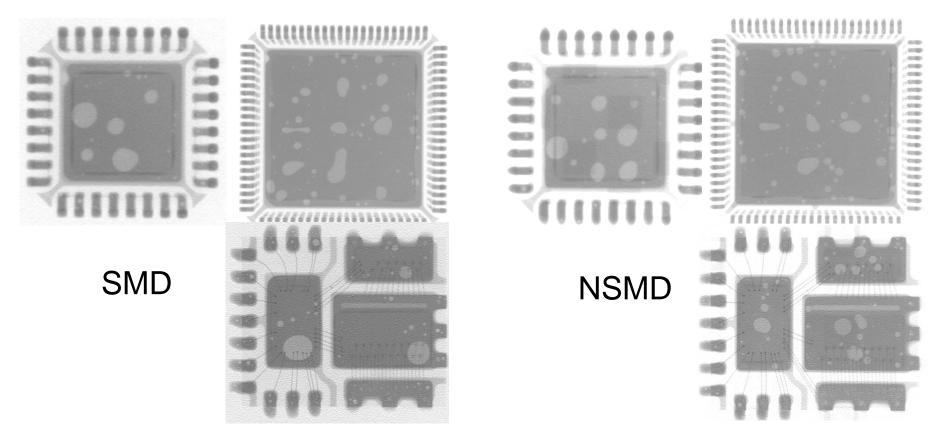

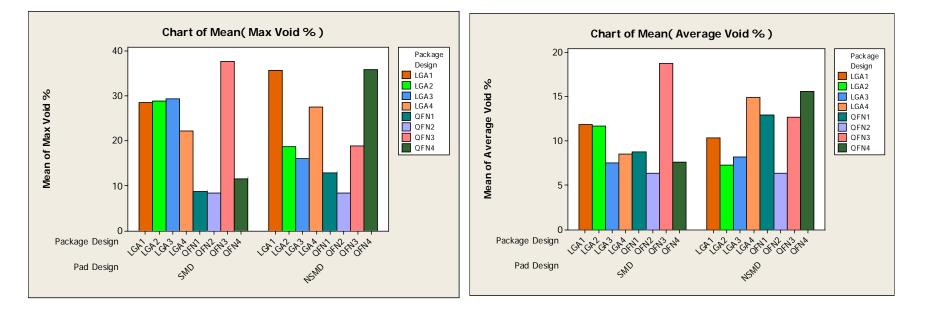

Generally speaking, there was no significant difference in voiding between solder mask defined (SMD) pad and non solder mask defined (NSMD) pad for BTC components (Figure 9). The result showed that the max void% did not change, but the average void% slightly increased for the NSMD pad as compared with the SMD pad. This difference was insignificant and varied based on the design of each BTC component. NSMD pads seemed to have more voids, but slightly smaller voids while SMD pads tended to have fewer but slightly larger voids (Figure 10). The selection of SMD or NSMD design should depend on each BTC package and its pad design (Figure 11). It was noticed that SMD pads resulted in more solder balls for some BTC packages as compared with NSMD pads, mostly with LGA (Figure 12). Solder balls were not commonly seen on QFN packages (Figure 12).

Figure 9 - The Impact of Pad Design on Voiding

As originally published in the IPC APEX EXPO Proceedings.

Figure 10 – X-Ray Image of QFN Components Designed Using SMD and NSMD Thermal Pad. a) SMD Pad b) NSMD Pad

Figure 11 – Voiding vs. Pad Design vs. Component Type. a) Comparison using maximum void percentage b) Comparison using average void percentage.

Figure 12 – Package Design vs. Solder Balls. LGA packages tend to have more solder balls than QFN packages.

#### Summary

There are many challenges with the assembly of BTC components. Solder joint voiding is the most common defect seen on all BTC components. It usually happens at the thermal pads of the device. The voiding behavior varies from BTC components to BTC components, and varies among the pads within the same component. This makes the quality assembly of BTC device more difficult. Many common process variables such as reflow temperature and reflow atmosphere do not affect voiding significantly; neither do the design variables (such as SMD or NSMD pad design). There is lack of standardization for the component pad design, and there are no industry criteria for voiding acceptance for BTC components. Further study on mitigating the common BTC quality concerns such as voiding and solder balling will be published in the future.

#### References

- 1. IPC-7093, "Design and Assembly Process Implementation for Bottom Termination SMT Components," March 2011.

- 2. Derrick Herron, Dr. Yan Liu, and Dr. Ning-Cheng Lee, "Voiding Control for QFN Assembly," SMTA Pan Pacific, 2011.

- 3. Richard Coyle, Heather McCormick, Peter Read, Richard Popowich, and Debra Fleming, "Temperature Cycling Performance of a Quad Flat No Lead (QFN) Package Assembled with Multiple Pb-Free Solders" *Proceedings of SMTAi* conference, 2003

# Assembly Challenges of Bottom Terminated Components

Jennifer Nguyen, David Geiger and Dongkai Shangguan, Ph. D.

> Flextronics International Milpitas, CA USA

## Contents

- Introduction

- BTC Challenges

- Test Vehicle

- Results and Discussions

- Conclusions

# What is BTC?

• BTC = Bottom Termination Components or Bottom Terminated Component.

2015

- BTCs includes various packages such as QFN (Quad Flat No Lead package), DFN (Dual Flat No Lead package), SON (Small Outline No-Leac package), LGA (Land Grid Array package) and MLF (Micro Lead-Frame package), etc...

- They are leadless components which terminations are protectively plated and are on the underside of the package

# Why BTC?

s originally published in the IPC APEX EXPO Proc

• Cost.

SI05 "O

- Low cost package, ideal for volume applications.

- Low profile package, light and thin.

- Ideal for handheld and consumer products.

- Good electrical performance

- Low resistance and capacitance due to no lead.

- Excellent thermal dissipation

- Large thermal pad in direct contact with PCB provides excellent heat transfer.

C16

As originally published in the IPC APEX EXPO Proceedings.

<u>Design</u>

IPC

- Uniqueness and Variation

- Most BTC components are unique from supplier to supplier and have their own pad design

s originally published in the IPC APEX EXPO Proce

<u>Assembly</u>

### •Tight Process Control

(PO" 2012

- A correct amount of solder is critical to having a good solder joint's quality and reliability.

- Excessive or unevenly deposited paste volume may cause package to float. Too little solder volume may cause defects (open, voiding, etc...)

### • Quality Issue

• Bridging, open, voiding, and solder balling are common defects.

**Inspection**

- X-ray inspection is required.

- The solder joint can be shadowed by the die attach pad or other components inside the package and results in unclear x-ray image and inaccurate voiding data.

- There is lack of equipment for automatic inspection. There is no "right" algorithm for many BTC packages.

- •There is no industry standard on the voiding criteria

- Some process issues such as solder balling and dewetting can escape from the automatic inspection program and have to be manually inspected.

s originally published in the IPC APEX EXPO Proce

### <u>Other</u>

### •Cleaning Issue

**PO**" 2012

- Low standoff height makes it difficult to remove flux residues.

- Reliability

- Reliability of the solder joint is controlled by solder amount (solder joint area and height)

- No leads that can take up stresses and strains.

- Voiding concern.

## Test Vehicle

s originally published in the IPC APEX EXPO Proce

XPO" 2012

Flextronics BTC Test Vehicle

Double sided board with the dimension of 8"x11"x0.093" [203mmx279mmx2.4mm]

- Include 13 different BTC designs from various suppliers.

# **BTC Test Vehicle Variables**

s originally published in the IPC APEX EXPO Proce

- Included 13 different types of BTC package.

- •Variables (built into PCB)

- Pad Design (3 levels): SMD, NSMD, Mixed

- Via Design:

XPO" 2012

- •With vias, no via

- •Via in pad, PTH via

- •Thermal Design

- •Trace connection (2 levels): with trace, no trace

- •Trace size (2 levels): 2 different trace sizes

- Ground plane (2 levels): 0.5oz, 1 oz.

- Orientation (3 levels): 0°, 45°, 90°

- Component spacings: various spacings.

# **Process and Fabrication Variables**

APEX EXPO P

Stencil thickness

2012

- Aperature opening

- Reflow profile (low, high)

- Reflow atmosphere (air, N2)

- Board thickness (93mil, 130mil)

- Board surface finish (OSP, I-Ag, ENIG)

- Solder mask thickness (1, 2 mil)

- Solder mask type (matt, glossy)

- Special process (pretin, preform, etc...)

- Baking

- Paste type (low voiding paste vs. regular paste)

- Lead-free vs. tin-lead process

# **DOE 1 Reflow Profiles**

| Η   | ia | h   |

|-----|----|-----|

| ••• | '9 | ••• |

|               | Low Profile |            | Hot Profile |           |

|---------------|-------------|------------|-------------|-----------|

| Locations     | Soak Time   | Peak Temp. | Soak Time   | Peak Temp |

| U100 (IP2004) | 85.75       | 236.06     | 140.54      | 245.93    |

| U309 (IP3837) | 82.48       | 243.9      | 139.69      | 253.56    |

| U703 (QFN32)  | 88.53       | 245.67     | 141.01      | 255.61    |

| U607 (DC-DC)  | 81.36       | 240.54     | 133.68      | 249.94    |

| U502 (LGA118) | 80.78       | 235.34     | 122.65      | 244.28    |

| U907(BGA196)  | 86.07       | 242.73     | 136.99      | 252.38    |

## **Temperature Impact**

Low profile, reflowed in air

High profile, reflowed in air

- Profile didn't have a significant impact on voiding.

- Voids slightly increased with higher temperature.

# Reflow Atmosphere Impact

High profile, reflowed in air

High profile, reflowed in N2

- Nitrogen didn't help to reduce voiding amount

- Nitrogen could result in less voids but larger voids.

## **Orientation Impact**

As originally published in the IPC APEX EXPO Proceedings.

-C16

APEX EXPO 2012

IPC

CANI

## SMD vs. NSMD Pad

• There was no significant difference in voiding between solder mask defined pad and no solder mask defined pad.

# SMD vs. NSMD Pad

As originally published in the IPC APEX EXPO Proce

XPO" 2012

IPC

• NSMD pads seemed to have more voids, but slightly smaller voids while SMD pads tended to have less voids, but lightly larger voids

# Component Type vs. Voiding

As originally published in the IPC APEX EXPO Proce

XPO" 2012

IPC

• Voids varied depending on the package type.

# **Design Impact**

### • LGA vs. QFN Type

### LGA Type

QFN Type

• More solder balls were seen on LGA packages. Solder balls were rarely seen QFN packages.

# Conclusions

s originally published in the IPC APEX EXPO Proce

- There are many challenges with the assembly of BTC components.

- Pad design variation

- Tight process window (paste volume and stencil design are critical)

- Inspection challenges (equipment capability, inspection time, data accuracy)

- Quality concerns (voiding, bridging, solder balling, floating, etc...)

- Reliability

XPO" 2012

- Solder joint voiding is the most common defect seen on all BTC components. The voiding behavior varies from BTC components to BTC components, and varies among the pads within the same component.

- Many common process variables such as reflow temperature and reflow atmosphere do not affect voiding significantly, neither do the design variables (such as SMD or NSMD pad design).

- There is lack of standardization for the component pad design, and there are no industry criteria for voiding acceptance for BTC components.

- Further study on mitigating the common BTC quality concerns such as voiding and solder balling will be published in the future.

# **Thank You**

## ?????